INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS™

INTERNATIONAL

ROADMAP

FOR

DEVICES AND SYSTEMS™

2024 IRDS

EXECUTIVE PACKAGING TUTORIAL (EPT)

CONSIDERATIONS FOR

HIGH PERFORMANCE COMPUTING AND

ARTIFICIAL INTELLIGENCE

*PART 1 – INTEGRATED CIRCUIT PACKAGING EVOLUTION*

THE IRDS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO

ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

© 2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Bluetooth® SIG and its members, licensors, and suppliers own all right, title, and interest (including intellectual property rights) in the Services, Content, and all draft and adopted specifications for the Bluetooth standard and reserve all rights not expressly granted to you in these Terms or, if applicable, the SIG Member Terms. The Bluetooth logos and word marks referenced in the Services and Content are the trademarks of Bluetooth SIG and its affiliates. Any other company names, product names, service names and logos referenced in connection with the Services or Content may be the trademarks of their respective owners.

Wi-Fi® and Wi-Fi Alliance® are registered trademarks of Wi-Fi Alliance.

The IEEE emblem is a trademark owned by the IEEE.

"IEEE", the IEEE logo, and other IEEE logos and titles (IRDS™, IEEE 802.11™, IEEE P1785™, IEEE P287™, IEEE P1770™, IEEE P149™, IEEE 1720™, etc.) are registered trademarks or service marks of The Institute of Electrical and Electronics Engineers, Incorporated. All other products, company names or other marks appearing on these sites are the trademarks of their respective owners. Nothing contained in these sites should be construed as granting, by implication, estoppel, or otherwise, any license or right to use any trademark displayed on these sites without prior written permission of IEEE or other trademark owners.

All product names, trademarks and registered trademarks are property of their respective owners. All company, product and service names used in this document are for identification purposes only. Use of these names, trademarks and brands does not imply endorsement. For the full listing of trademark statements, please visit <https://ieee.org/>.

## Table of Contents

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| Overview .....                                                                  | 1  |

| 1. Relationship Between Transistor Switching Speed and Interconnect Delay ..... | 4  |

| The Challenge of Reducing Signal Propagation Delay.....                         | 6  |

| Typical Values of Signal Propagation Delays .....                               | 7  |

| Why System on Chip (SoC)?.....                                                  | 7  |

| Cost Implications of SoC Development and Adoption .....                         | 9  |

| Packaging Considerations of SoC and SiP.....                                    | 11 |

| Conclusion .....                                                                | 12 |

| First ETP Summary—System on Chip .....                                          | 12 |

| 2. Electronic Packaging Overview.....                                           | 13 |

| Summary of Packaging Technologies.....                                          | 13 |

| Conclusion .....                                                                | 16 |

| Second ETP Summary—Packaging Evolution .....                                    | 16 |

| 3. Packaging Substrates Overview.....                                           | 17 |

| Substrate Materials .....                                                       | 17 |

| Take-away .....                                                                 | 19 |

| Evaluation of Electronic Packaging Substrate Alternatives .....                 | 20 |

| Conclusion .....                                                                | 21 |

| Third EPT Summary—Substrate Materials and Manufacturing Processes.....          | 22 |

| 4. Grid Array Technologies.....                                                 | 22 |

| Land Grid Array.....                                                            | 22 |

| Ball Grid Array .....                                                           | 23 |

| Conclusion .....                                                                | 25 |

| Fourth EPT Summary—Grid Arrays .....                                            | 25 |

| 5. Flip Chip Technology .....                                                   | 26 |

| Flip Chip History .....                                                         | 26 |

| Flip Chip Packaging Fundamentals .....                                          | 27 |

| Applications of Flip Chip Packaging .....                                       | 28 |

| Brief History of Evolutions of Bump Composition in Flip Chip .....              | 29 |

| Flip Chip Materials .....                                                       | 31 |

| Flip Chip Bump Spacing (Pitch) Requirements.....                                | 32 |

| Conclusion .....                                                                | 35 |

| Miniaturization of Bumps for Flip Chip .....                                    | 35 |

| Fifth ETP Summary—Flip Chip evolution .....                                     | 36 |

| 6. Single Die versus Multi-Chips Assembly Module (MCM) .....                    | 37 |

| Single Die Configuration .....                                                  | 37 |

| Multi-Chip Configuration .....                                                  | 38 |

| Overview of System in Package (SiP) .....                                       | 39 |

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Multi-Chip Module Assembly .....                                                    | 41 |

| MCM Interconnections to Board .....                                                 | 41 |

| Summary of Typical SiP Technologies .....                                           | 42 |

| 3D Chips Stacking Thermal Management .....                                          | 43 |

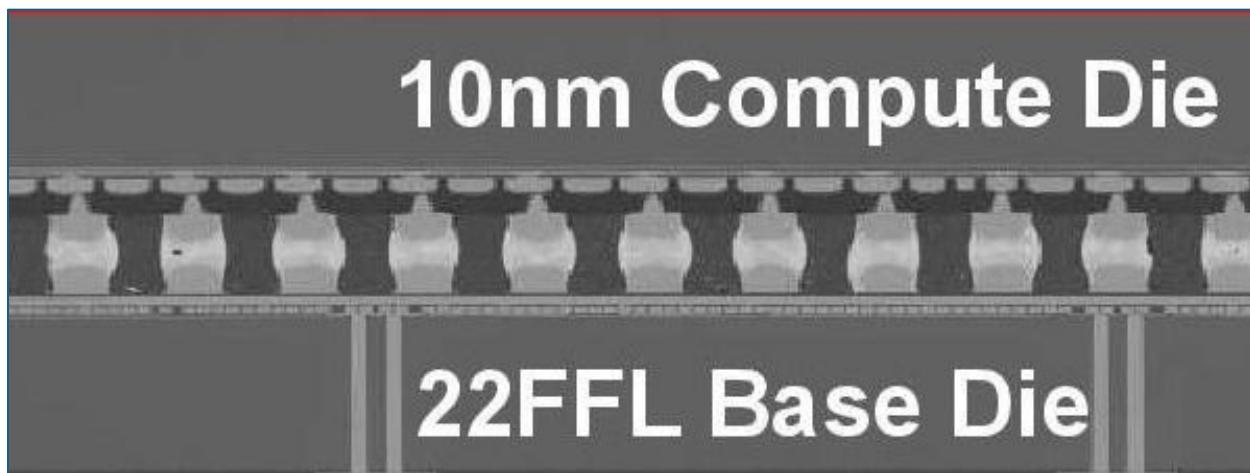

| Micropillars.....                                                                   | 45 |

| Flip Chip and Micropillars.....                                                     | 47 |

| Through Silicon Vias .....                                                          | 48 |

| TSV Application in 3D stacking .....                                                | 50 |

| Conclusion .....                                                                    | 52 |

| Micropillars and TSV roles in SiP .....                                             | 52 |

| Sixth ETP Summary—System in Package.....                                            | 54 |

| 7. SiP Role in Reducing Signal Propagation Delay (SPD) .....                        | 55 |

| Historical Trends of Signal Propagation Delay and Interconnect Density in SiP ..... | 56 |

| Some practical examples of actual SiP packaging technologies .....                  | 60 |

| Seventh ETP Summary—Signal Propagation Delay .....                                  | 60 |

| 8. Dynamic Power Consumption in ICs and Its Impact on Temperature and Leakage.....  | 61 |

| Thermal Considerations And Management Techniques.....                               | 64 |

| Force Air and Water Cooling .....                                                   | 67 |

| 8 <sup>th</sup> ETP Summary—Thermal Limits and Management.....                      | 73 |

| Concluding Remarks .....                                                            | 73 |

| Glossary/Abbreviations .....                                                        | 74 |

| Appendices .....                                                                    | 76 |

| Appendix A—Substrate Packaging Sizes and the Substrate Fabrication Process .....    | 76 |

| Appendix B—Land Grid Array Packaging Fabrication Process.....                       | 79 |

| Appendix C—Ball Grid Array Fabrication and Electrical Connection Processes .....    | 80 |

| Appendix D—Flip Chip Packaging Fabrication Process .....                            | 81 |

| Appendix E—Flip Chip Manufacturing Process .....                                    | 82 |

| Appendix F—MCM Assembly Process .....                                               | 83 |

| Appendix G—Substrate Preparation Process for Multi-Chip Assembly .....              | 84 |

| Appendix H—Micropillars Fabrication Process .....                                   | 85 |

| Appendix I—TSV Fabrication Process.....                                             | 86 |

| Appendix J—Practical examples of actual SiP packaging technologies.....             | 87 |

## List of Figures

|                                                                                             |    |

|---------------------------------------------------------------------------------------------|----|

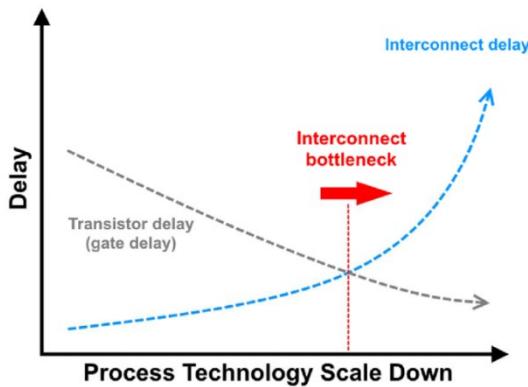

| Figure 1. Qualitative comparison of transistor delay and interconnect delay .....           | 4  |

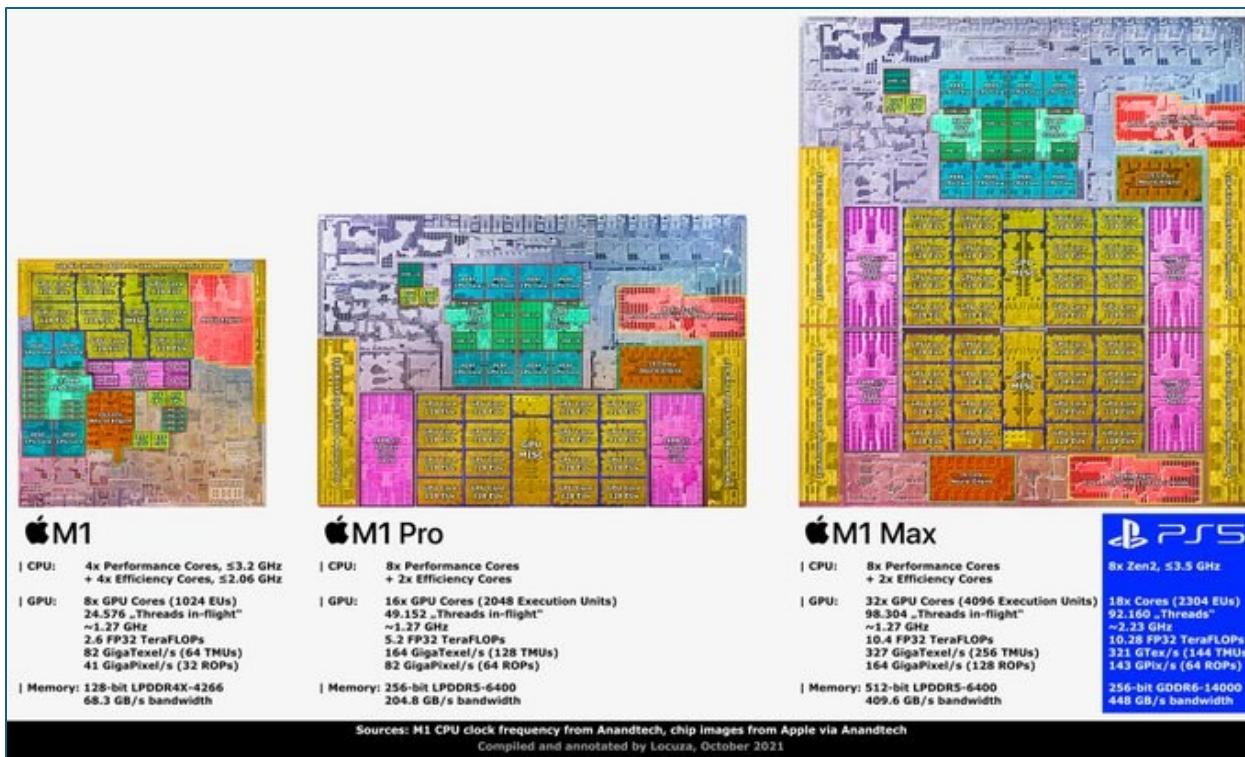

| Figure 2. Examples of Apple System on Chip .....                                            | 8  |

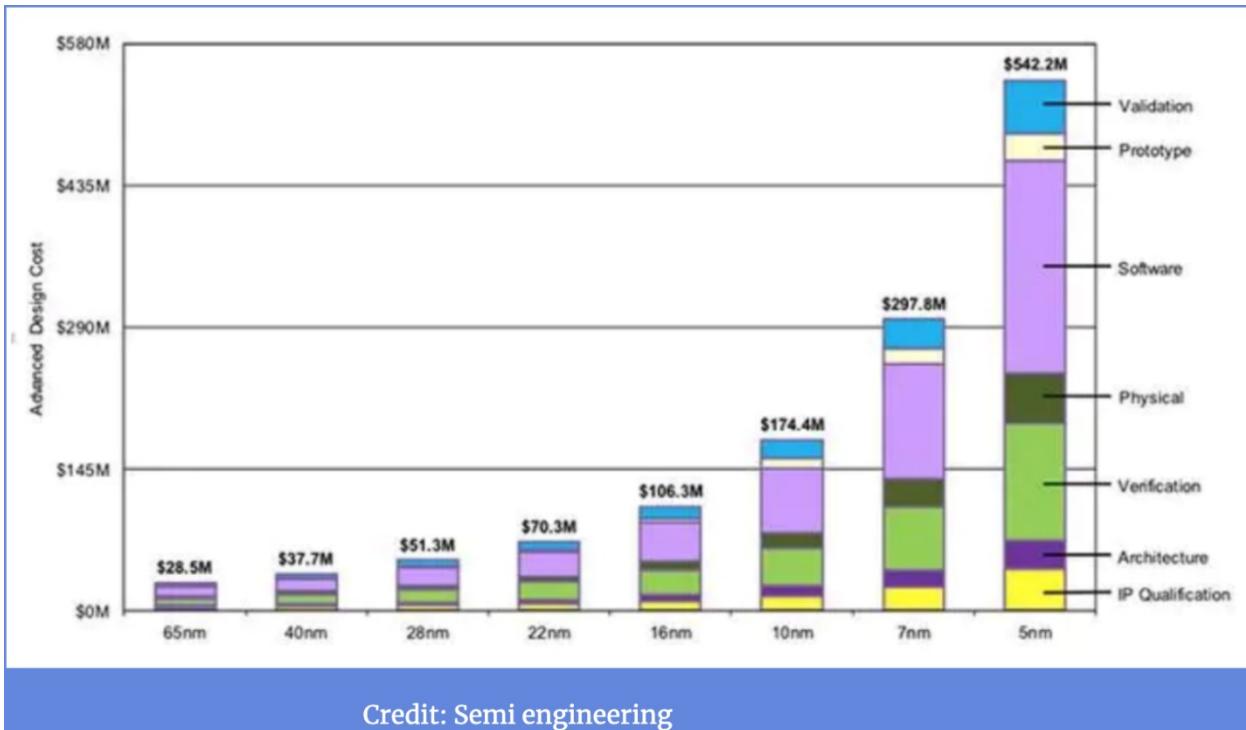

| Figure 3. Total Cost Associated with SoC Product Design.....                                | 11 |

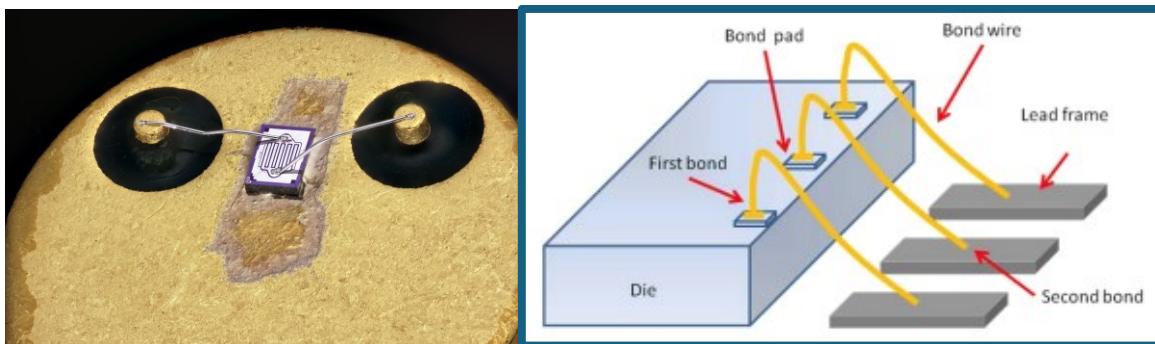

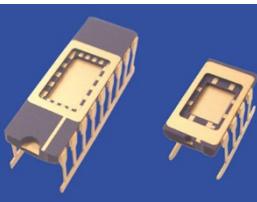

| Figure 4. Early Wire Bond Packaging Solutions .....                                         | 13 |

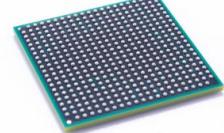

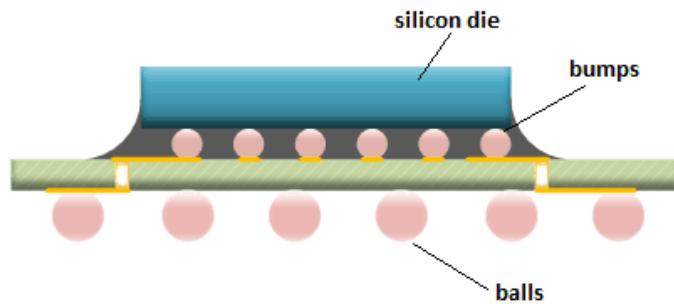

| Figure 5. Example of BGA package .....                                                      | 24 |

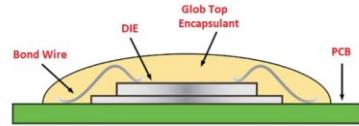

| Figure 6. Example of Flip Chip packaging on substrate .....                                 | 28 |

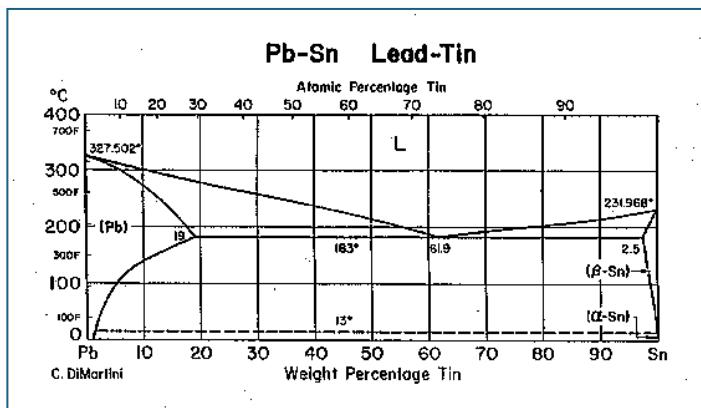

| Figure 7. Phase diagram of Pb-Sn showing composition vs. collapse temperature .....         | 29 |

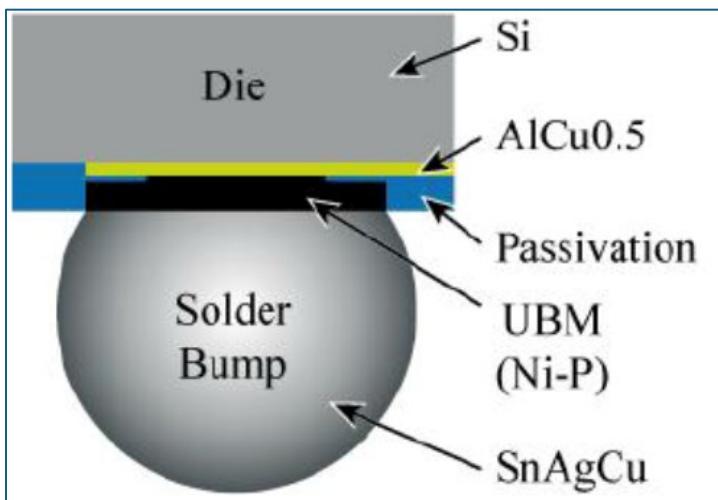

| Figure 8. Modern bump composition.....                                                      | 30 |

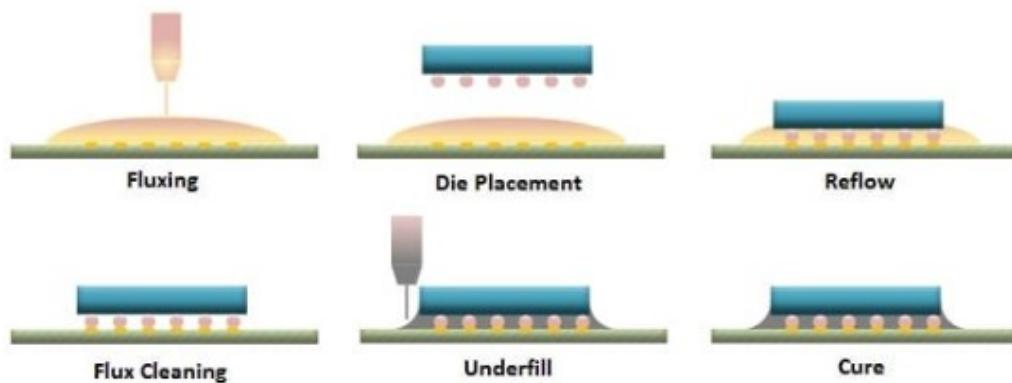

| Figure 9. Step-by-step schematic overview of the fabrication of the flip chip process ..... | 31 |

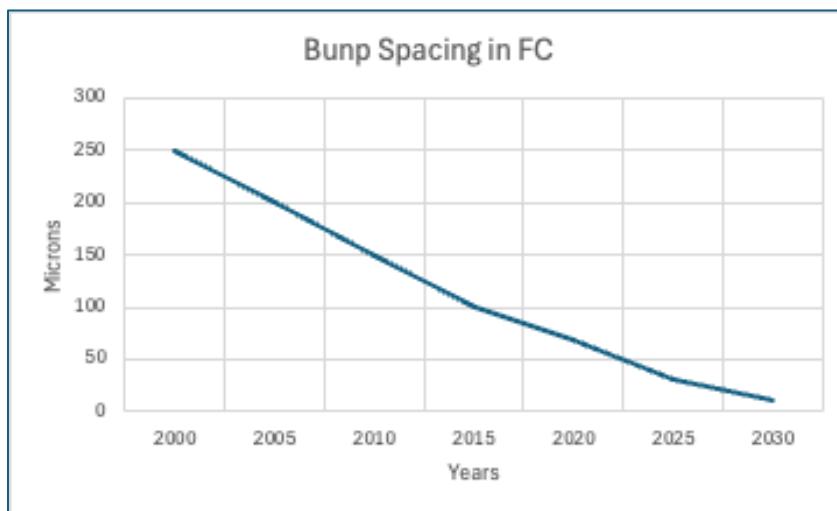

| Figure 10. Historical trend of bump spacing and forecast .....                              | 35 |

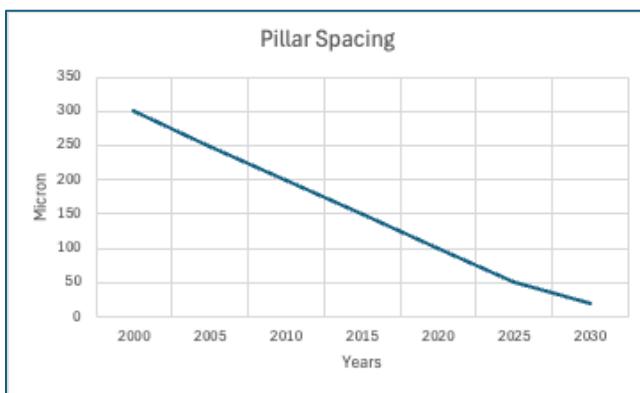

| Figure 11. Historical trend of pillar spacing and future forecast.....                      | 47 |

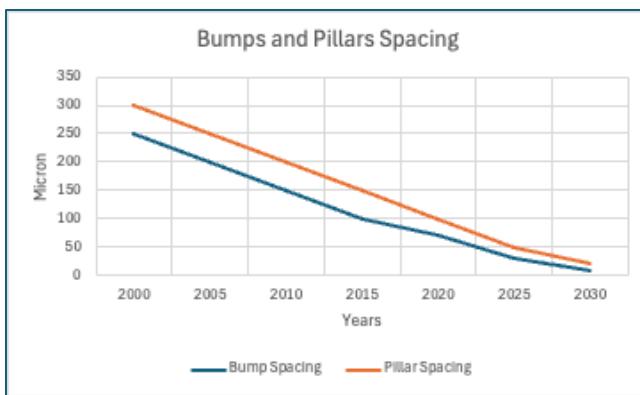

| Figure 12. Historical trend of Bump and Pillar spacing and future forecast .....            | 49 |

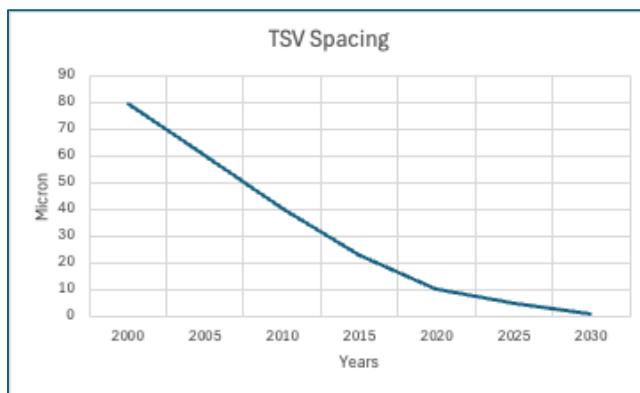

| Figure 13. Historical trends in TSV spacing and future forecast .....                       | 51 |

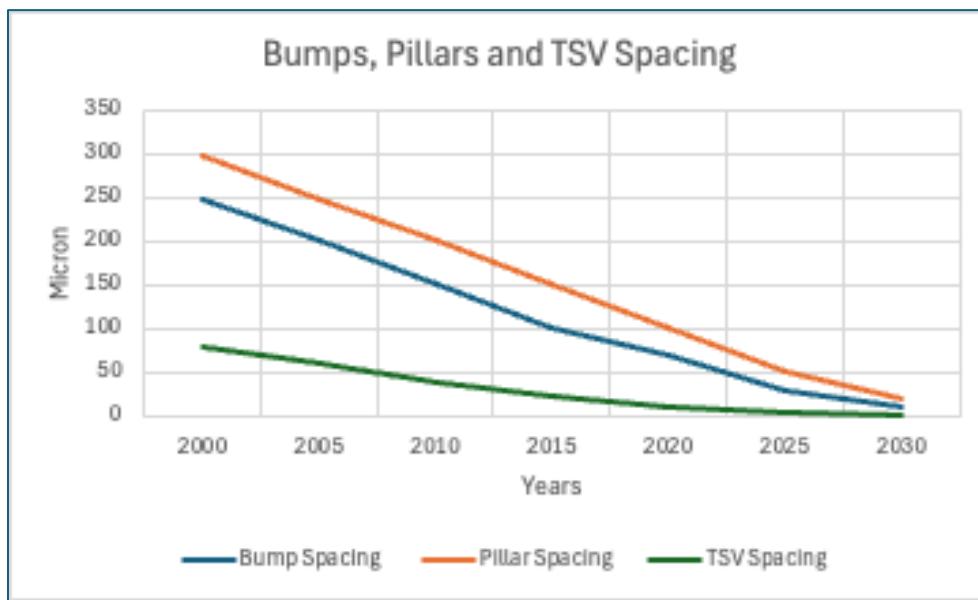

| Figure 14. Historical trends of Bumps, Pillars and TSV spacing and future forecast .....    | 53 |

| Figure 15. Schematic example of 3D integration in SiP .....                                 | 54 |

| Figure 16. Key components contributing to SPD in modern packages.....                       | 57 |

| Figure 17. Relation between SPD and interconnect density .....                              | 58 |

| Figure 18. Dynamic power consumption as a function of supply voltage .....                  | 61 |

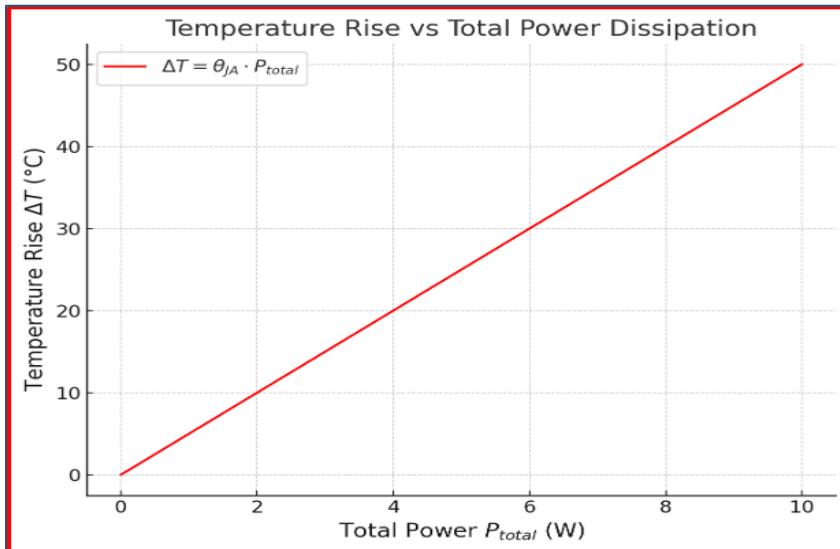

| Figure 19. Temperature increase as a function of power.....                                 | 62 |

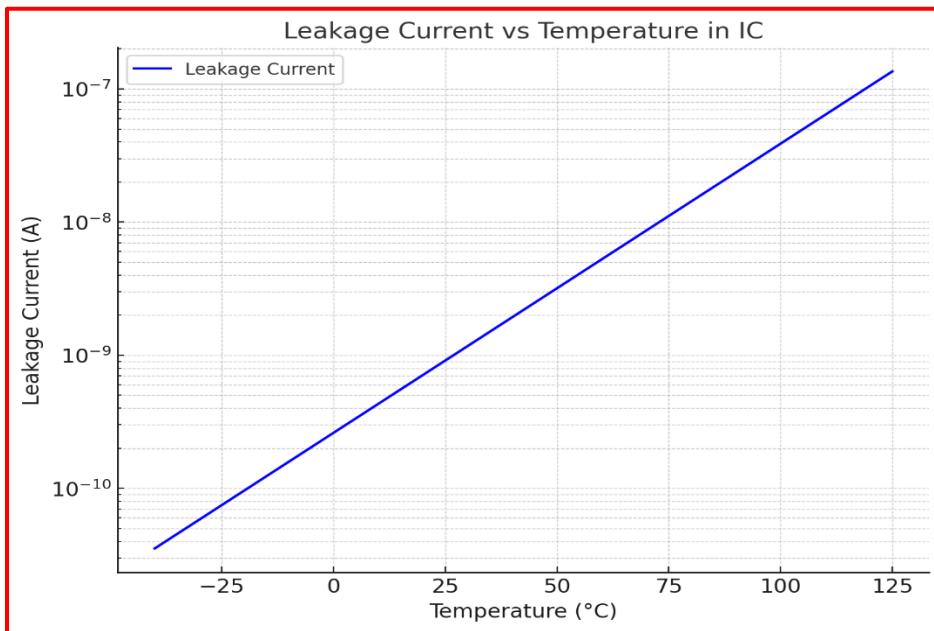

| Figure 20. Leakage increase as a function of temperature .....                              | 63 |

| Figure 21. Example of air cooling of semiconductor boards .....                             | 69 |

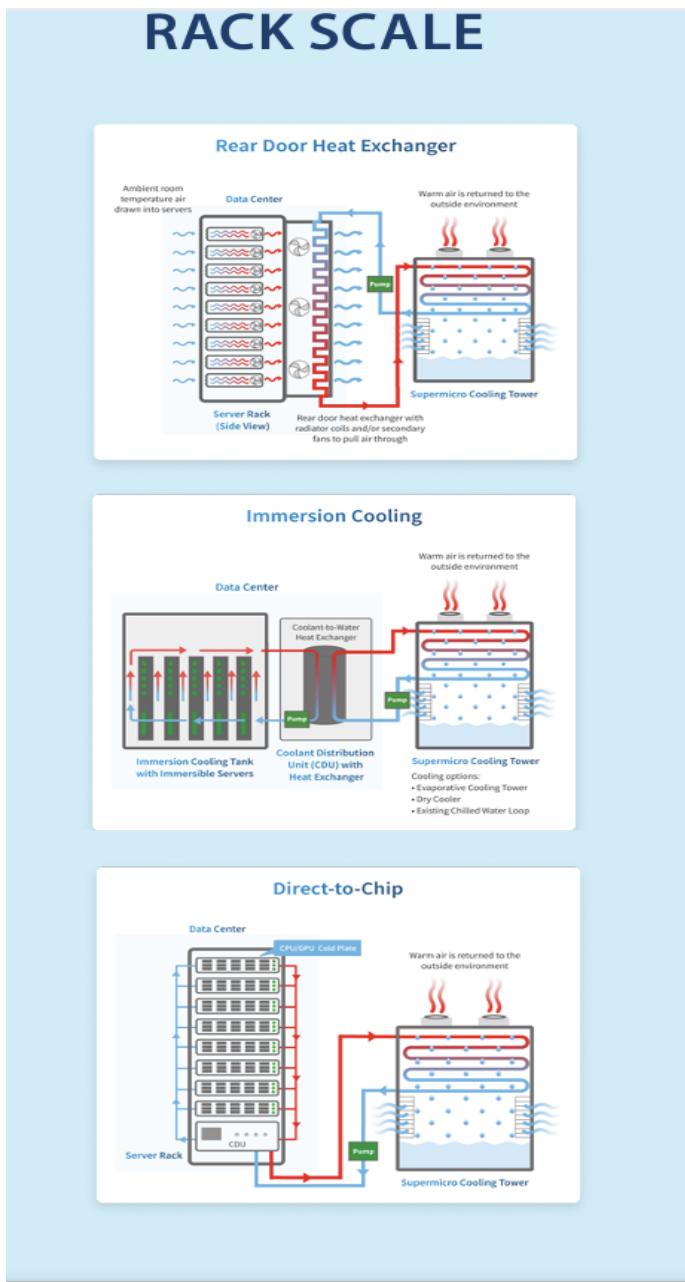

| Figure 22. Schematic example of water cooling of boards in a AI rack .....                  | 70 |

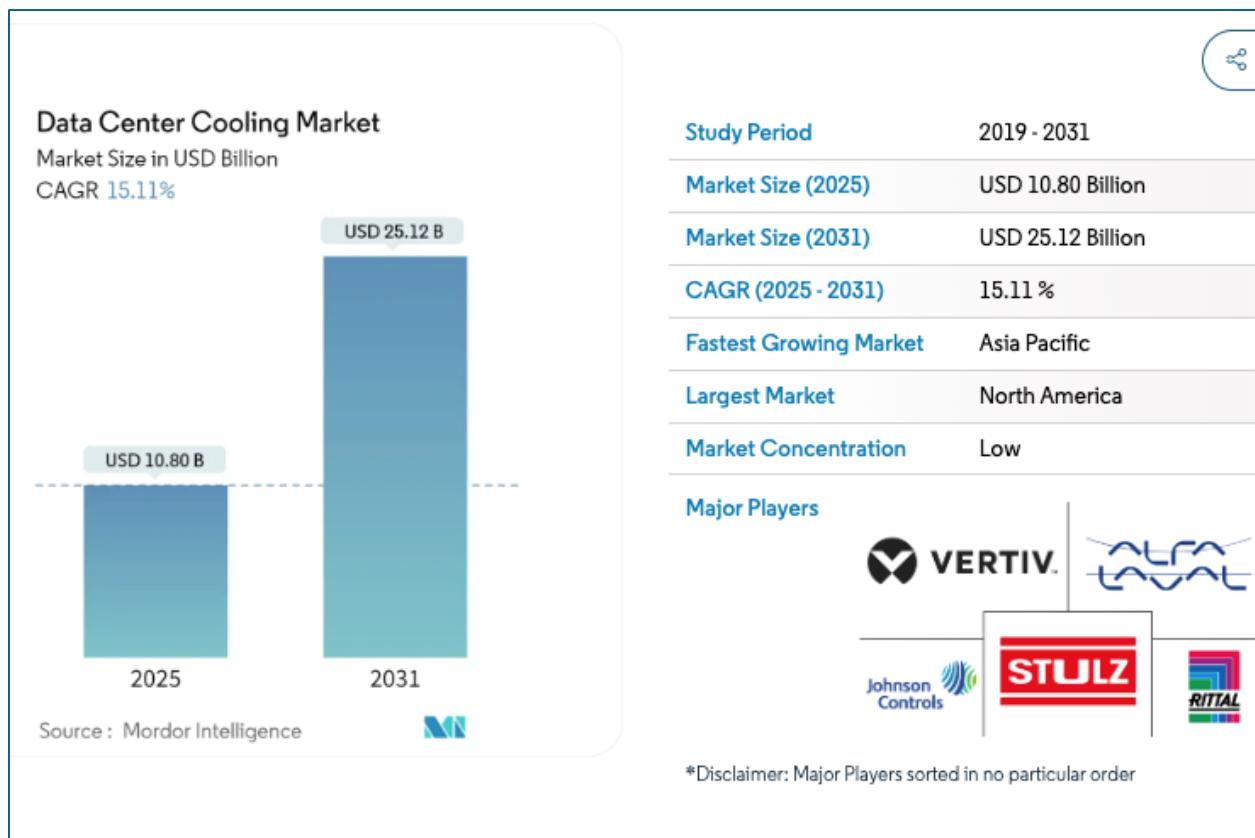

| Figure 23. Projected data center cooling market size.....                                   | 72 |

## List of Tables

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Table 1. Solutions to Mitigate Interconnect Delay.....                              | 5  |

| Table 2 Considerations for Signal Delay Analysis.....                               | 6  |

| Table 3. Overview of typical signal propagation delays .....                        | 7  |

| Table 4. Implications of Development and Adoption Cost Type .....                   | 9  |

| Table 5. Key areas involved in electronics packaging .....                          | 13 |

| Table 6. Major semiconductor packaging technologies and their main features.....    | 14 |

| Table 7. Substrate Types and Applications.....                                      | 17 |

| Table 8. Main Building Blocks of Substrate Manufacturing Process .....              | 18 |

| Table 9. Advantages and Disadvantages of Substrate Types.....                       | 21 |

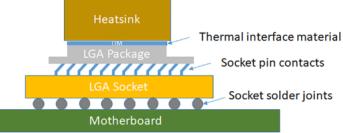

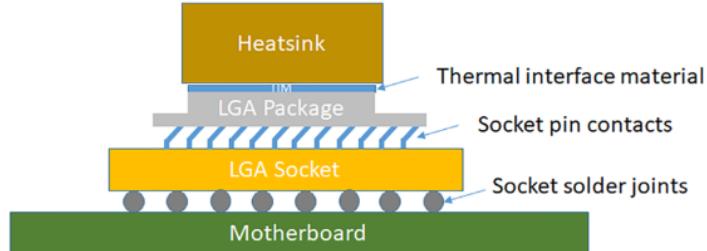

| Figure 5. Example of LGA package mounted on motherboard and including heatsink..... | 22 |

| Table 10. Advantages and Disadvantages of LGA Packaging .....                       | 23 |

| Table 11. Ball Grid Array Packaging Advantages and Disadvantages .....              | 24 |

| Table 12. Advantages and Disadvantages of Flip Chip Packaging .....                 | 28 |

| Table 13. Advantages of Flip Chip Technology .....                                  | 30 |

| Table 14. Flip chip process elements materials and purpose .....                    | 31 |

| Table 15. Bump Spacing Trends for Micro-level Packaging .....                       | 35 |

| Table 16. Advantages and Disadvantages of Single Die Configuration.....             | 37 |

| Table 17. Advantages and Disadvantages of Multi-Chip Configuration.....             | 38 |

| Table 18. TSV Benefits and Challenges.....                                          | 49 |

| Table 19. SiP Technology Benefits in SPD Reduction.....                             | 55 |

| Table 20. Use of Capacitors and Inductors in SiP .....                              | 59 |

| Table 21. Advanced Packaging Thermal Solutions.....                                 | 65 |

| Table 22. Comparison of Forced Air and Water Cooling .....                          | 67 |

| Table 23. IC Encapsulation Process Tailored for Water Cooling .....                 | 71 |

| Table A1. Typical sizes for different types of packaging substrates.....            | 76 |

| Table A2. Substrate Packaging Process Steps .....                                   | 77 |

| Table A3. LGA fabrication process .....                                             | 79 |

| Table A4. Ball Grid Array Fabrication Process .....                                 | 80 |

| Table A5. BGA Electrical Connection Process .....                                   | 80 |

| Table A7. Flip Chip Manufacturing Process .....                                     | 82 |

| Table A8. MCM Assembly Process .....                                                | 83 |

| Table A9. MCM Substrate Preparation Process for Multi-Chip Assembly .....           | 84 |

| Table A10. Micropillars Fabrication Process .....                                   | 85 |

| Table A11. Fabrication of TSVs.....                                                 | 86 |

## DISCLAIMER

To provide realistic and tangible understanding of multi-chip module (MCM) technologies the Executive Packaging Tutorial (EPT) has collected information derived from some of the most commonly available examples existing in the market to fulfill a realistic tutorial function. It is not the goal of the EPT to endorse or advertise any of these MCM approaches. Furthermore, since the assessment of these MCMs is done on the basis of publicly available information it is possible that the original suppliers may have additional knowledge and information that could change some of the assessments reported in the EPT. It is recommended that readers seeking additional insight on any of the reported MCM approaches and related subjects should be contacting the suppliers to obtain the most reliable information.

Finally, many of the MCM potential benefits and potential issues are reported on a case-by-case approach. These statements represent a technical opinion of the EPT and should not be construed as benchmarking assessments since no experimental verification has been conducted in preparing this report. In addition, none of the assessments expressed for any specific MCM approach should be used as a benchmarking reference when comparing one MCM approach to another.

# INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS (IRDS)

## EXECUTIVE PACKAGING TUTORIAL PART 1

Integrated Circuit Packaging Evolution

## Overview

It is the purpose of this Executive Packaging Tutorial (EPT) to shed some light on the adoption, evolution and transformation of multi-chip modules (MCMs) in the era of high-performance computing (HPC) and artificial intelligence (AI) to help the reader to better comprehend the drivers and the roles of the fundamental building blocks of this technology revolution in a neutral and objective way.

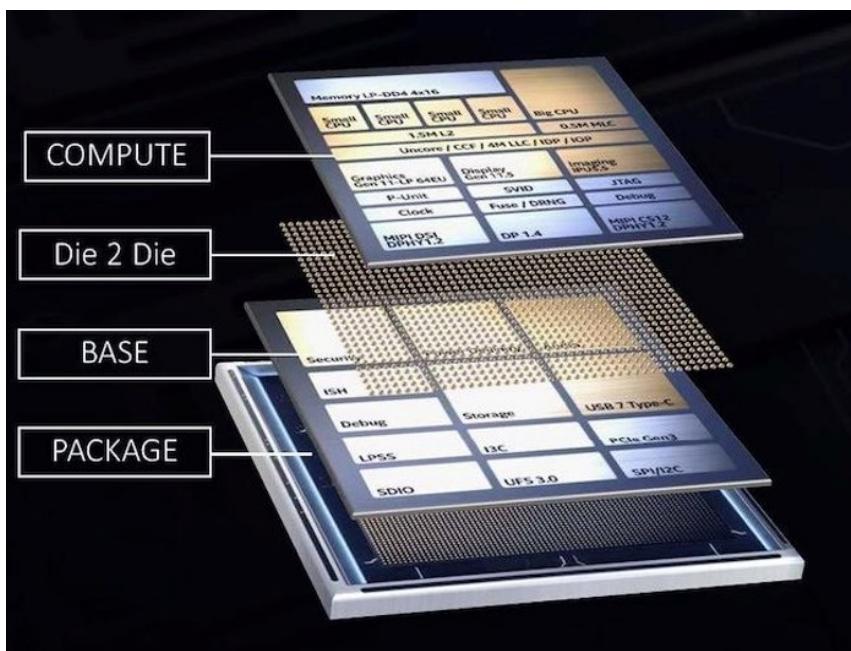

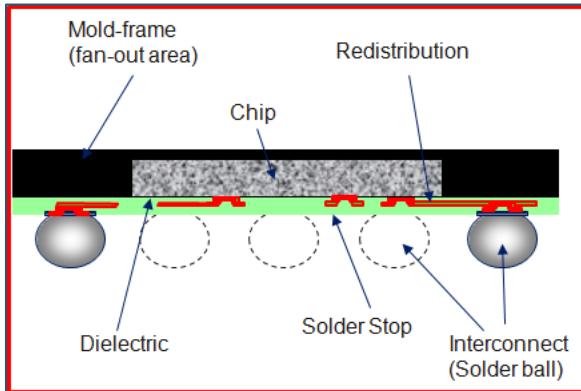

This tutorial is providing a broad overview of the fast-evolving field of packaging. Until five years ago system on chip (SoC) products provided an adequate level of transistor integration necessary to realize a variety of multi-functional building blocks on a single chip meeting the requirements of the most advanced systems. The requirements of fast evolving HPC and AI systems have however outpaced the rate at which the required functionalities can be realized on a single die. This situation has re-energized packaging technologies developed as far back as 50 years ago for high performance but then prohibitively expensive systems. Presently, all the leading system integrators rely on packaging technologies to co-locate multiple dice in a single package (SiP) and multiple closely connected MCM in a single board. New packaging technologies have also been developed and deployed to accelerate an increased level of integration at the package and board levels. Many companies have developed proprietary nomenclatures to describe their own solutions. It is the purpose of this tutorial to provide a neutral overview of the field of advanced packaging.

Most of all the EPT consists in outlining step-by-step a major shift in packaging technology initially driven by HPC and presently accelerated by AI. Personal computers (PCs) and smart phones were the drivers of the electronics industry for the past 40 years. Their selling prices hovered in the range of thousands of dollars. Consequently, analysis of the bill of materials (BOM) documented that cost of the each of the integrated circuits spanned from a few dollars to tens of dollars. This limited allocation of dollars to each of the IC products consequently demanded to maintain the cost of packaging in the cents/pin range. To accomplish this goal packaging manufacturing was transferred overseas early on (i.e., mid-seventies) to mainly benefit from the low-cost of labor.

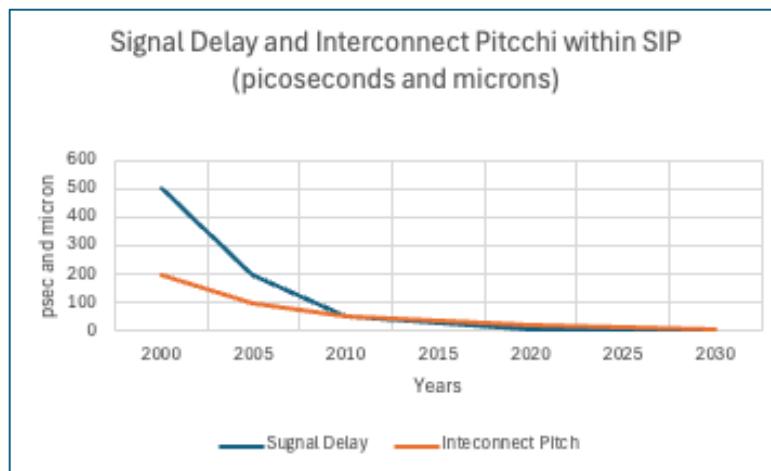

The cost of the packaging materials were also closely monitored and minimized. Packaging materials evolved from costly ceramic materials to plastic encapsulation to currently “organic” packaging substrates, just to mentioned a few. The downside of all these low-cost solutions resides in the implication that signal propagation delay resulted severely degraded right after the signal left the IC due to poor propagation properties of all the materials used for the in-package interconnections related to their intrinsic electrical properties. To partially circumvent this problem, multiple system in package technologies known at the time as multi-chip modules were developed about 30 years ago and used for very expensive HPC systems. New MCM applications were rediscovered in recent years driven by AI applications. SiP consists mainly in co-locating memory chips next to logic chips on the substrate of a single package; by so doing overall space occupied by the components is minimized as compared to connecting several individually packaged chips co-located on the same board. This design results in signal propagation delays being reduced due to shorter lengths of interconnections (from cm to mm).

Discussions about further reducing the effect of the package organic substrate on interconnect delays are evolving towards the development of glass substrates to provide better performance. This is perfectly reasonable based on a packaging driven solution, but this is where it is necessary to make a major departure from traditional approaches depending on the type of product.

*The HPC and the AI worlds are presently undergoing a major transition from central processing unit (CPU)-driven HPC computational data centers to graphical processing unit (GPU)-driven AI data centers.*

The basic building block of a datacenter is represented by the server “rack” whose price becomes the reference performance and cost benchmark to be compared to PCs and mobile phones prices. For example, a Blackwell-powered rack may cost up to several millions of dollars! Analyzing the price of a data center and going down the supply chain looking at the key components of a rack reveals that a Bella board may cost hundreds of thousands of dollars. A Blackwell chip may be priced up to \$20,000 to \$70,000!

*In this case also, any reduction in signal propagation delay remains essential and if a comparison is made to accomplish this goal between the ratio of traditional IC cost to packaging cost it becomes clear that tens and even hundreds of dollars can be allocated to the cost of an HPC or AI package.*

*With this realization it is necessary to abandon the world of low-cost driven packaging world and step into the HPC/AI-driven world of leading-edge expensive wafer manufacturing to get the right answer!*

Recently, the concept of power delivery from the backside of an IC has been demonstrated (backside power distribution (BPD)) and several companies have announced plans to implement that technology. Additionally, the intention of distributing clock signals from the backside (backside clock (BC)) of a CPU or a GPU have been reported. This is realized by manufacturing these capabilities on a “partially sacrificial” wafer and then “thinning and peeling” the surface of this wafer where the innovative BPD and clock distribution circuitry is built. After these initial process steps, “bonding” the thinned down and peeled wafer surface to the backside of the microprocessor unit (MPU) or GPU wafer yields the desired structural configuration.

Furthermore, it appears that other active devices can be implemented in the sacrificial wafer since it is amenable to be produced with any leading-edge technology. With this realization it then appears clear that by optimizing the thickness of the thinned-down support wafer it is possible to extend its role to becoming the substrate of the whole SiP! This approach would also provide additional benefits. For instance, thermal compatibility between the upper chip and the chip bonded on the backside would be ensured since both are made of silicon. In addition, multiple levels of interconnections could be fabricated on this new silicon substrate to connect all the other chips located in the SiP with substantial reduction of signal propagation delays.

The cost of this complex substrate produced by leading-edge silicon technology would likely escalate in the hundreds of dollars or more, but it should be remembered that the combined, integrated dice are selling for tens of thousands of dollars! This realization revisits the 60s to 90s era in the industry in which only system companies could afford the adoption of expensive flip chip packaging technology. This is because this cost disappeared in the overall cost of the system that was rewarded by very handsome selling prices in the ten thousands and hundred thousands of dollars.

## Packaging History

Encapsulation of transistors was devised early in IC design and manufacturing to prevent any damage to the frail structure of transistors during handling. Connections from ICs to package were accomplished by bonding gold wires first to the aluminum bond pads of the IC by ultrasonic welding and then connecting these bond wires onto gold pads located inside the package case. Once the die was fully encapsulated within the package shell, elongated pins protruding from the bottom or side of the package and connected to the package bond pads were then inserted in a socket located on a printed circuit board (PCB). Electrical signals generated by individual transistors and later on by integrated circuit (IC) were connected via metallic traces located on the surface of the board to other components placed on the same PCB.

As time went by, the number of transistors and complexity of ICs kept on increasing and consequently die size increased. To accommodate for the increased number of signals exiting the ICs it became necessary to evolve the package to a dual in-line structure to accommodate for pins on two sides. Eventually the package evolved to a square format with pins on all four sides to maximize the number of available inputs/outputs for electrical and mechanical connections. During this evolution to more connections, the role of packaging remained limited to physical protection of ICs and as electrical conduits to the board and systems, thus mainly as a rather passive element. However, things drastically changed in the past 20 years as the role of packaging surged to the level of an active solution provider. The most dramatic example to illustrate this point occurred in 2011.

Qualcomm and Xilinx were both competing for market share in field-programmable gate array (FPGA) technology, these products were characterized by very large die sizes. Both companies relied on outside sources for the silicon wafers manufacturing. The die size of FPGA had kept on further increasing therefore progressively and drastically reducing the number of dice produced on each wafer due to both die size and die yields; conjunctively the 28 nm technology available on the market at the time was rather immature and it was not fully adequate to support both performance and yields required for FPGA. However, when technology by itself is not sufficient to solve a problem, it is time for creative engineering solutions. Xilinx made the insightful decision to split the large die into two dice. These were located side by side into the same package but electrically connected with each other so that operated as a single large die. It is well known that for a given number of defects the yields of smaller dice are higher than the yields of an equivalent die twice the area. Furthermore, the absolute amount of leakage and other deleterious effects were more manageable by partitioning the die into two dice. In the end this approach called 2.5D was successful and prevailed in the marketplace; for the first time the crucial role of advanced packaging stood up and forever changed the role of packaging from a passive participant to an active enabler. It was then said that packaging solutions could

provide contributions to the final product by providing introduction of a “*half technology node generation*” ahead of schedule.

It soon become clear that this first step in novel packaging technology was only the beginning of an intense integration between dice and packages in providing the most viable and timely system-oriented solutions.

In 2014 the various teams of the International Technology Roadmap for Semiconductors (ITRS) effort—realizing that many transformations in IC manufacturing were underway—warned that major changes were coming in the electronics industry, such as new IC/package roles. The ITRS identified that the relationship between systems, integrated circuits, and packages was becoming symbiotically intermingled going forward.

Due to this realization the ITRS reassembled the seventeen highly specialized technology working groups (TWGs) existing at the time into seven integrated focus teams (IFTs). The first reports of this new organization were published in the 2015 ITRS2.0. Among the newly created chapters a forward-looking chapter entitled “Heterogeneous Integration” was published and for the first time provided a novel view of the many integrated packaging and IC solutions coming in the next 15 years. It was expected that initially *homogeneous integration* of electronics components (i.e., chips based on similar silicon technologies) were going to populate the system in package world and then evolve into more complex ones in the subsequent 10-15 years. Within this projected timeline an era of truly heterogenous integration of ICs (created with fundamentally different technologies) was to occur starting with the year 2025; as such, this process is just beginning.

As predicted by the ITRS in 2015 and subsequently by the IRDS, the interaction and symbiosis between ICs and packages has continued to synchronically and homogenously increase and as a result multi-chip modules have now become fundamental building blocks in the manufacture of any high-performance electronics system. Many companies have created their own approach and *self-defined nomenclature*, and, even though some differences exist, it can be shown that fundamentally these are all variations on the same technology.

## The Approach to the Executive Packaging Tutorial

This EPT has been assembled in three parts. Each one of them is essentially “self-contained.” This approach allows the knowledgeable reader to advance to the section of their interest without necessarily reading several of the previous sections. This approach comes at a price since it creates some intrinsic redundancy but provides the benefit to the reader of “self-contained” sections. Therefore, the readers should be aware that this is not an editorial failure but it is motivated by a necessary level of redundancy.

This part of the EPT provides a brief overview of packaging technologies. However, it is not intended to represent an encyclopedia of packaging. The main purpose of Part 1 is to outline the features and evolution of packaging technologies leading to system in package for HPC and AI. However, this cannot be done ignoring the evolution of system on chip (SoC). A more extensive analysis of SoC is provided in the 2024 IRDS Executive Summary, and it is recommended that the two documents are evaluated side by side.

In order to make the content more easily readable many additional details are provided in the appended material for further insights. Details for process steps and examples of technologies are appended for elaboration purposes.

# 1. Relationship Between Transistor Switching Speed and Interconnect Delay

The relationship between transistor switching speed and interconnect delay is crucial in determining the overall performance of integrated circuits. As transistor switching speeds increase, the impact of interconnect delay becomes more significant, eventually becoming the limiting factor in circuit performance. Understanding this relationship and exploring solutions to minimize interconnect delay is essential for advancing performance of semiconductor technologies. Table 1 provides solutions to mitigate interconnect delay.

Figure 1. Qualitative comparison of transistor delay and interconnect delay

## The Challenge of Signal Propagation Delay

### 1. Transistor Switching Speed

- **Definition**—Transistor switching speed refers to the time it takes for a transistor to switch between its on (conducting) and off (non-conducting) states. This speed is often measured in terms of the gate delay or the rise and fall times of the transistor.

- **Influence on Circuit Speed**—The faster a transistor can switch, the higher the potential clock frequency of a circuit, leading to faster data processing and overall performance.

### 2. Interconnect Delay

- **Definition**—Interconnect delay is the time it takes for a signal to propagate through the metal wires (interconnects) that connect different components within an IC. This delay is influenced by the resistance (R) and capacitance (C) of the interconnect, often referred to as the RC delay.

- **Significance**—As time went by transistors have become faster and therefore more numerous and overall longer interconnects have made interconnect delay the major bottleneck in achieving higher circuit speeds. In few words, even if transistors will continue to switch at increasingly higher speeds, the overall performance will be limited by the time it takes for signals to travel through the interconnects.

### 3. Increasing Disparity

- **Scaling Challenges**—With transistor sizes shrinking (following Moore's Law), transistor switching speeds have increased. Concurrently, interconnects have scaled down also leading to both increased resistance (reduced cross section) and increased capacitance (closer line to line spacing) leading to higher RC values per unit length. This results in a growing disparity where interconnect delay becomes more pronounced compared to transistor switching speed.

**Table 1. Solutions to Mitigate Interconnect Delay**

| Solution                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Material Innovations</b>               | <ul style="list-style-type: none"> <li>Low-k Dielectrics—Using low-k dielectric materials between interconnects reduces the capacitance, thereby reducing the RC delay. This has been a common approach in modern semiconductor manufacturing.</li> <li>Copper Interconnects—Replacing aluminum with copper as the interconnect material reduces resistance, as copper has lower resistivity. This change helps to reduce the overall interconnect delay.</li> </ul>                                                                                                                                     |

| <b>Advanced Interconnect Design</b>       | <ul style="list-style-type: none"> <li>3D Integration and through-silicon vias—Three-dimensional (3D) integration using TSVs can significantly reduce the length of interconnects by allowing vertical stacking of circuits. This reduces the overall interconnect delay by shortening the distance signals need to travel.</li> <li>Interconnect Spacing and Width—Optimizing the width and spacing of interconnects can help manage resistance and capacitance, reducing delay. Wider interconnects reduce resistance, while increased spacing reduces capacitance.</li> </ul>                         |

| <b>Signal Repeater Insertion</b>          | <ul style="list-style-type: none"> <li>Repeaters—Placing repeaters (buffers) at intervals along long interconnects can reduce delay by boosting the signal and mitigating the RC delay. This technique breaks a long interconnect into shorter segments, each with reduced delay.</li> <li>Optimal Placement—The placement of repeaters must be optimized to balance the benefits of delay reduction with the power and area overhead they introduce.</li> </ul>                                                                                                                                         |

| <b>Design Techniques</b>                  | <ul style="list-style-type: none"> <li>Clock Tree Optimization—The clock distribution network, or clock tree, can be optimized to minimize skew and delay. Techniques like balanced clock trees or the use of low-skew clock buffers help ensure that all parts of the circuit receive the clock signal simultaneously.</li> <li>Timing-Driven Layout—During the physical design phase, timing-driven layout tools can be used to optimize the placement and routing of components to minimize critical path delays, including those caused by interconnects.</li> </ul>                                 |

| <b>Signal Integrity Management</b>        | <ul style="list-style-type: none"> <li>Shielding and Guard Rings—Implementing shielding (ground or power wires adjacent to signal lines) can reduce crosstalk and noise, improving signal integrity and reducing delay variability.</li> <li>Differential Signaling—Using differential signaling, where two complementary signals are transmitted, can improve noise immunity and reduce the impact of delay variations.</li> </ul>                                                                                                                                                                      |

| <b>On-Chip Networks and Architectures</b> | <ul style="list-style-type: none"> <li>Network-on-Chip (NoC)—In complex multi-core processors, NoC architectures can be used to manage data flow between cores more efficiently, reducing the impact of interconnect delays. These networks are designed to handle the communication between cores with minimal latency.</li> <li>Chiplet Architectures—Chiplet-based designs, where a system is divided into smaller, interconnected chiplets, can optimize interconnects within each chiplet and between them, reducing overall delay.</li> </ul>                                                      |

| <b>Emerging Technologies</b>              | <ul style="list-style-type: none"> <li>Optical Interconnects—Optical interconnects, which use light instead of electrical signals to transmit data, offer the potential for much higher speeds with lower delay over long distances. While still in development, they represent a promising solution for future high-performance ICs.</li> <li>Carbon Nanotubes and Graphene—These materials offer lower resistance and higher electron mobility compared to traditional metals, potentially reducing interconnect delay if they can be reliably integrated into semiconductor manufacturing.</li> </ul> |

## Take Away

The relationship between transistor switching speed and interconnect delay is a critical factor in modern IC design. While transistors have continued to get faster, interconnect delay has become the most significant challenge. Solutions

such as material innovations, advanced interconnect design, insertion of signal repeater, and the adoption of new technological and structural solutions are essential to mitigating interconnect delay and unlocking the full potential of fast-switching transistors. These approaches will help ensure that IC performance will keep pace with the increasing demands for better performance of modern HPC, AI and internet of things (IoT) communication systems.

## The Challenge of Reducing Signal Propagation Delay

Signal delay analysis in ICs is a crucial aspect of circuit design, ensuring that signals propagate through the IC in a timely manner to meet performance and reliability requirements. An overview of key concepts and methods involved in signal delay analysis include types of delay, factors affecting signal delay, delay models, tools and techniques, and optimizing strategies. See Table 2.

**Table 2 Considerations for Signal Delay Analysis**

| Key Concepts                          | Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Types of Delay</b>                 | <ul style="list-style-type: none"> <li>Propagation Delay—The time it takes for a signal to travel from the input to the output of a logic gate or circuit element.</li> <li>Setup Time—The minimum time before the clock edge that the data input must be stable to ensure correct operation.</li> <li>Hold Time—The minimum time after the clock edge that the data input must remain stable to ensure correct operation.</li> </ul>                                                                                                                                                                                                        |

| <b>Factors Affecting Signal Delay</b> | <ul style="list-style-type: none"> <li>Capacitance—The parasitic capacitance associated with the wiring and transistor gates affects delay. Increased capacitance slows down the signal.</li> <li>Resistance—The resistance of the metal interconnects can also cause delays. Higher resistance leads to increased delay.</li> <li>Transistor Characteristics—The size of transistors (width and length) and their threshold voltages impact how quickly they can switch, affecting delay.</li> <li>Load—The load connected to the output of a gate or circuit affects the delay. Larger loads generally result in longer delays.</li> </ul> |

| <b>Delay Models</b>                   | <ul style="list-style-type: none"> <li>RC Delay Model—This simple model approximates delay based on the resistance (R) and capacitance (C) of the interconnects. It's often used for quick estimations.</li> <li>Logical Effort—This method involves analyzing how a gate's delay scales with the number of stages and the effort required to drive a load. It helps in optimizing circuit performance.</li> <li>Elmore Delay Model—An extension of the RC model that provides a more accurate delay estimation by considering distributed capacitance.</li> </ul>                                                                           |

| <b>Tools and Techniques</b>           | <ul style="list-style-type: none"> <li>SPICE Simulations—Used to simulate the detailed delay characteristics of ICs based on the actual circuit design and component models.</li> <li>Static Timing Analysis (STA)—A method used to verify that the circuit meets timing requirements under all possible conditions. STA checks all possible paths in the circuit to ensure signals are properly synchronized.</li> <li>Dynamic Timing Analysis—Examines timing under real operating conditions, including variability and environmental factors.</li> </ul>                                                                                 |

| <b>Optimization Strategies</b>        | <ul style="list-style-type: none"> <li>Sizing—Adjusting the width of transistors to balance delay and power consumption.</li> <li>Pipelining—Breaking down long combinational paths into shorter stages separated by flip-flops to reduce delay.</li> <li>Buffer Insertion—Adding buffers in long interconnect paths to reduce delay by driving the load more efficiently.</li> </ul>                                                                                                                                                                                                                                                        |

| <b>Critical Path Analysis</b>         | <ul style="list-style-type: none"> <li>Identifying the longest path through the circuit that determines the maximum clock frequency. Ensuring this path meets the timing requirements is crucial for reliable operation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>Impact of Technology Scaling</b>   | <ul style="list-style-type: none"> <li>As technology nodes shrink, delays in ICs can become more significant due to increased resistance, capacitance, and variations in manufacturing. Advanced analysis and optimization techniques are required to handle these challenges effectively.</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

## Take Away Message

Signal delay analysis in IC design involves understanding and managing various factors that affect how quickly signals propagate through a circuit. By employing accurate models and sophisticated tools, designers can optimize performance and ensure that the IC meets all timing requirements.

## Typical Values of Signal Propagation Delays

Signal propagation delays vary significantly depending on the material, distance, and specific technology used. Table 3 shows a general overview of typical signal propagation delays, as follows:

**Table 3. Overview of typical signal propagation delays**

| Type                                 | Propagation Delay                                 | Details                                                                                                                                                                                                                                                                                                               |

|--------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Integrated Circuits</b>           | 10 ps/mm to 100 ps/mm                             | In ICs, delays depend on the type of semiconductor technology (CMOS, BiCMOS, etc.), the complexity of the logic gates, and the interconnect length within the chip. Advanced nodes (e.g., 7nm, 5nm) tend to have lower delays due to shorter gate lengths and higher operating frequencies.                           |

| <b>Packages</b>                      | 50 ps/mm to 150 ps/mm                             | The delay in a package is influenced by the type of package (e.g., wire-bonded, flip-chip, or ball grid array), the length of the interconnections, and the dielectric material used. For high-speed designs, package delay is a critical factor.                                                                     |

| <b>Printed Circuit Boards (PCBs)</b> | 140 ps/inch to 180 ps/inch (55 ps/cm to 70 ps/cm) | The delay on PCBs is influenced by the trace length, the dielectric material (FR-4, Rogers, etc.), and the trace width. High-speed PCBs are designed with controlled impedance to minimize delay and signal degradation.                                                                                              |

| <b>Backplanes</b>                    | 140 ps/inch to 180 ps/inch (55 ps/cm to 70 ps/cm) | Backplanes are like PCBs but generally handle higher signal densities and longer distances. The propagation delay is usually like that of PCBs, but the length of traces in backplanes can lead to higher overall delay.                                                                                              |

| <b>Trays and Racks (Cabling)</b>     | 5 ns/m to 6 ns/m                                  | In data center environments, signal propagation delays over cabling in trays and racks are influenced by the type of cable (e.g., coaxial, twisted pair, optical fiber). Optical cables have lower delays (~5 ns/m) compared to copper cables, and they also suffer less from signal attenuation over long distances. |

| <b>Fiber Optics</b>                  | ~5 ns/m                                           | Optical fibers are used in high-speed communication due to their low latency and high bandwidth. The delay is approximately 5 ns/m due to the speed of light in fiber being slightly slower than in a vacuum.                                                                                                         |

## Why System on Chip?

### Motivations and Drivers for System on Chip Development

The development and adoption of multiple and novel system on chip technologies have been historically driven by several motivations that focus on enhancing performance, reducing overall size of packaged die on PCBs, and improving efficiency. These motivations are key to meeting the demands of modern electronic devices, especially in areas like mobile computing, consumer electronics, and IoT where space is limited.

Figure 2. Examples of Apple System on Chip

### Integration and Miniaturization

- **Increased Functionality**—SoCs integrate multiple components (such as CPUs, GPUs, memory, communication interfaces, and power management) onto a single chip.

- This integration allows for greater functionality in a smaller form factor, which is essential for mobile devices, wearables, and other compact electronics.

- **Reduced Size and Weight**—By consolidating multiple discrete components into a single chip, SoCs significantly reduce the overall size and weight of electronic devices.

- This is particularly important in industries where space is at a premium, such as aerospace, medical devices, and consumer electronics.

### Power Efficiency

- **Lower Power Consumption**—SoCs are designed to optimize power usage by integrating power-efficient components and using advanced power management techniques.

- This is critical for battery-powered devices, where energy efficiency directly impacts battery life.

- **Improved Thermal Management**—With fewer discrete components and shorter interconnections, SoCs generate less heat compared to multi-chip solutions.

- This improves thermal performance, reducing the need for complex cooling solutions.

### Performance Enhancements

- **Optimized Communication**—By integrating all components on a single chip, SoCs reduce the need for external interconnections, leading to faster data transfer rates and lower latency.

- This improves overall system performance, especially in applications that require real-time processing.

- **Specialized Processing Units**—SoCs often include specialized processing units, such as AI accelerators, digital signal processors (DSPs), and graphics processing units.

- These units are optimized for specific tasks, enhancing the performance of applications like machine learning, image processing, and gaming.

### Cost Reduction

- **Reduced Bill of Materials (BOM)**—By consolidating multiple functions into a single chip, SoCs reduce the number of components needed on the printed circuit board.

- This leads to lower material costs and simplifies the supply chain.

- **Simplified Manufacturing**—SoCs reduce the complexity of the PCB design and assembly process. With fewer components to place and connect, the manufacturing process becomes more streamlined, leading to lower production costs and faster time-to-market.

- **Lower Packaging and Assembly Costs**—Integrating components into a single chip reduces the need for multiple packaging solutions, further cutting costs associated with assembly and testing.

### Design Flexibility and Customization

- **Tailored Solutions**—SoCs can be customized to meet the specific needs of an application or market.

- This flexibility allows companies to differentiate their products by integrating proprietary technologies or optimizing the chip for particular use cases.

- **Faster Innovation Cycles**—The ability to integrate new features and technologies into a single chip accelerates product development cycles.

- This is crucial in fast-moving markets like consumer electronics, where staying ahead of competitors is vital.

### Market Demands and Trends

- **Mobile and IoT Growth**—The explosion of mobile devices, IoT, and connected devices drives the demand for SoCs. These markets require compact, energy-efficient solutions that can deliver high performance in small, portable form factors.

- **AI and Edge Computing**—The increasing adoption of AI and edge computing applications has fueled the development of SoCs with integrated AI accelerators and other specialized processing units.

- This enables devices to perform complex computations locally, reducing the need for cloud-based processing.

## Cost Implications of SoC Development and Adoption

While SoCs offer significant advantages in terms of performance, power efficiency, and integration, their development and adoption come with certain cost implications that companies must consider. See Table 4.

**Table 4. Implications of Development and Adoption Cost Type**

| Development and Adoption Cost Type | Implications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>High Development Costs</b>      | <ul style="list-style-type: none"> <li>• <b>Complex Design Process</b>—Designing an SoC is a highly complex and resource-intensive process. It involves significant investment in research and development (R&amp;D), specialized design tools, and skilled engineers. The cost of developing an SoC can be substantial, particularly for cutting-edge technologies.</li> <li>• <b>IP Licensing and Integration</b>—SoCs often require the integration of third-party intellectual property (IP) blocks, such as cores for CPUs, GPUs, and communication interfaces. Licensing these IP blocks can add to the overall cost of SoC development.</li> </ul> |

| <b>Expensive Manufacturing</b>     | <ul style="list-style-type: none"> <li>• <b>Advanced Semiconductor Processes</b>—SoCs are typically manufactured using advanced semiconductor processes, such as 7nm, 5nm, or even smaller nodes. These processes are expensive due to the complexity of</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |

| Development and Adoption Cost Type | Implications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | <ul style="list-style-type: none"> <li>the technology, the need for specialized fabrication facilities, and lower yields associated with cutting-edge processes.</li> <li>Testing and Validation—Comprehensive testing and validation are crucial for ensuring the reliability and performance of an SoC. This requires sophisticated testing equipment and methodologies, which can add to the manufacturing costs.</li> </ul>                                                                                                                                                                                             |

| <b>Economies of Scale</b>          | <ul style="list-style-type: none"> <li>High Initial Investment—The initial investment in SoC development and manufacturing is high. However, companies can achieve economies of scale by producing large volumes of SoCs, which helps spread the fixed costs over a larger number of units, reducing the per-unit cost.</li> <li>Volume Production—To fully benefit from economies of scale, companies need to ensure high-volume production and strong demand for the SoC. Achieving this requires successful market penetration and widespread adoption of the devices that use the SoC.</li> </ul>                       |

| <b>Risk of Obsolescence</b>        | <ul style="list-style-type: none"> <li>Rapid Technological Advancements—The semiconductor industry evolves rapidly, with new process nodes, IP blocks, and design techniques continually emerging. SoCs developed today may become obsolete quickly, requiring continuous investment in new designs and technologies.</li> <li>Market Shifts—Market demand for specific features or applications can change rapidly. An SoC tailored for a particular use case may face reduced demand if market trends shift, leading to potential losses if the SoC does not achieve expected sales volumes.</li> </ul>                   |

| <b>Long Development Cycles</b>     | <ul style="list-style-type: none"> <li>Time-to-Market Pressure—Developing an SoC takes time, and delays in the development process can lead to missed market opportunities. Companies need to carefully manage the development timeline to ensure that the SoC is ready for market introduction at the right time.</li> <li>Design Iterations—The complexity of SoC design often requires multiple design iterations, each of which adds time and cost to the development process. Companies must balance the need for thorough testing and validation with the pressure to bring the product to market quickly.</li> </ul> |

## Conclusion

The motivations and drivers for SoC development are rooted in the need for reducing the space occupied by the IC by means of higher integration while improving performance, providing better power efficiency, and enabling cost reduction in modern ICs.

While SoCs offer numerous advantages, their development and manufacturing come with significant costs. Companies must carefully consider these cost implications, including high development expenses, manufacturing costs, and the risks associated with rapid technological changes and market dynamics.

Despite these challenges, the benefits of SoCs often outweigh the costs, making them a crucial technology in the ongoing evolution of electronics.

Figure 3. Total Cost Associated with SoC Product Design

## Packaging Considerations of SoC and SiP

System-on-Chip packaging has evolved significantly since the concept of integrating multiple components onto a single chip first emerged. The following includes a brief overview of the history and development of SoC packaging:

### Early Beginnings (1980s - 1990s)

- **Early Integration**—The concept of integrating multiple functions onto a single chip began in the 1980s with the rise of microcontrollers and early ASICs (Application-Specific Integrated Circuits). Initially, integration was limited to a few components, and packaging techniques were relatively simple, primarily using dual in-line packages (DIPs) and surface-mount packages.

- **Advancements in ASICs**—The 1990s saw the growth of more complex ASICs with higher levels of integration. These ASICs combined several functions onto a single chip and the associated packaging technology was progressively evolving, with packages like quad flat packages (QFPs) and ball grid arrays (BGAs) becoming more common.

### Rise of SoCs (2000s)

#### *Homogeneous Integration*

- **Defining the SoC**—The term “System-on-Chip” became more prominent in the 2000s as semiconductor manufacturers began integrating entire systems, including processors, memory, I/O interfaces, and other components onto a single chip. This integration led to significant improvements in reduce PCB occupancy, improved performance and better power efficiency.

- **Advanced Packaging Techniques**—As SoCs became more complex, advanced packaging techniques were developed to manage the increased number of connections and reduce the overall footprint. Techniques in addition to wire bonding such as flip-chip bonding, and the use of advanced BGAs became common. Multi-chip modules were also used to combine multiple die in a single package.

## Modern SoC Packaging in SiP (2010s - Present)

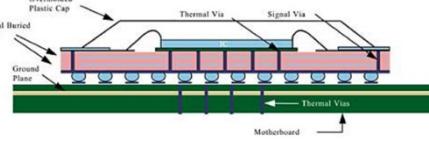

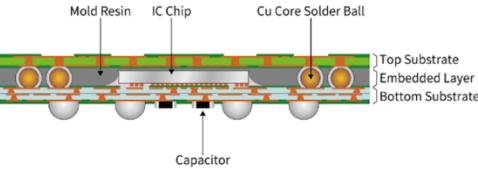

- **3D Packaging and Integration**—The 2010s saw the introduction of 3D packaging technologies, such as Through-Silicon Vias and stacked die configurations. These technologies allowed for greater integration density and improved performance by reducing signal latency and power consumption.

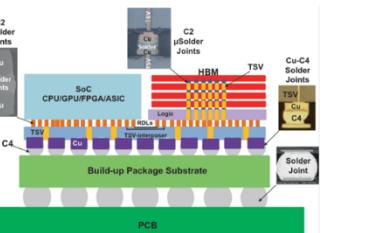

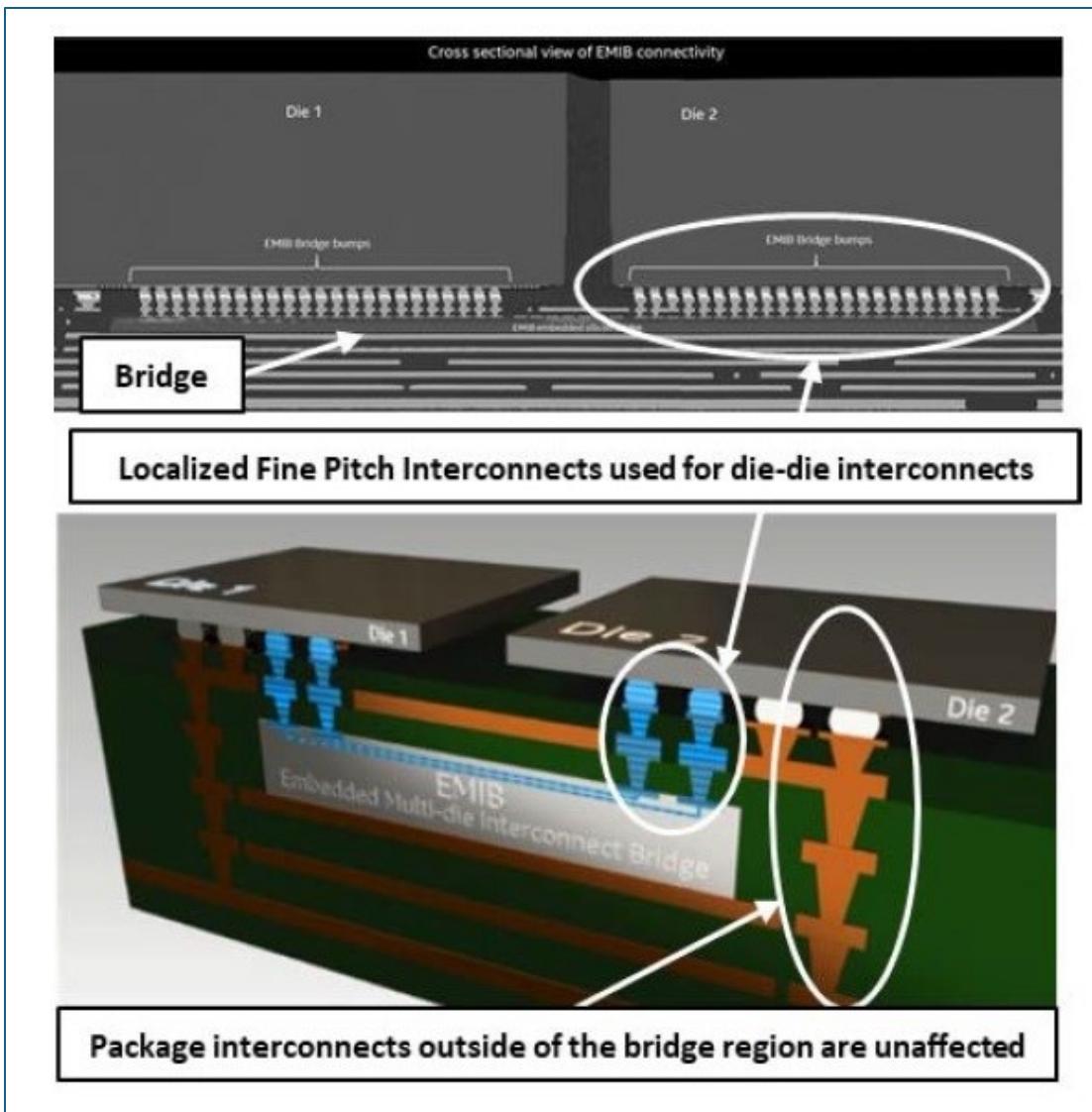

- **Advanced Substrates and Interposers**—The use of advanced substrates and interposers became more widespread. Technologies like Silicon Interposers and Embedded Multi-Die Interconnect Bridge (EMIB) provided high-bandwidth interconnects between different parts of the SoC or between the SoC and other components.

- **System-in-Package**—The concept of System-in-Package, which typically involves homogeneous integration of multiple logic and memory chips into a single package, became more common in the past 10 years. SiP allows also for the integration of various functionalities, such as RF components, sensors, and memory, alongside the main SoC.

- **Chiplet Architectures**—More recently, the industry has been moving towards chiplet-based architectures. This approach involves creating many small, modular chips (chiplets) that can be combined in a single package to create a versatile and scalable SoC. This method helps in managing design complexity and costs.

## Future Trends

- **Heterogeneous Integration**—The future of SoC packaging is bound to eventually evolve from homogeneous integration and focus on heterogeneous integration, where different types of chips produced with multiple diverse technologies (e.g., III-V, GaN, Ge and other drastically different technologies) are integrated into a single package or module. This approach aims to further enhance performance, power efficiency, and functionality.

- **Advanced Materials and Techniques**—Ongoing research into new materials, such as advanced thermal interfaces and high-k dielectrics, as well as new packaging techniques, will continue to drive the evolution of SoC packaging, allowing for even higher integration densities and better performance.

## Conclusion

Overall, the history of SoC packaging reflects the continual drive towards greater integration, higher performance, and improved efficiency, driven by the demands of modern electronic devices and applications. These requirements have prompted also the adoption of packaging technologies pioneered more than 30 years ago by system houses into consumers' applications.

## First ETP Summary—System on Chip

SoCs presently integrate multiple homogeneous silicon-based components—such as CPUs, GPUs, memory, communication interfaces, and power management—onto a single chip. This integration allows for greater functionality in a smaller form factor. By consolidating multiple discrete components into a single chip, SoCs significantly reduce the overall size and weight of electronic devices. SoCs are designed to optimize power usage by integrating power-efficient components and using advanced power management techniques. This is critical for battery-powered devices, where energy efficiency directly impacts battery life. With fewer discrete components and shorter interconnections, SoCs generate less heat compared to multi-chip solutions. This improves thermal performance, reducing the need for complex cooling solutions.

*But most of all by integrating multiple components on a single chip, SoCs reduce signal propagating delay and reduces the need for package-to-package interconnections, leading to faster data transfer rates and lower latency. This improves overall system performance, especially in applications that require real-time processing and minimal latency. These SoC accomplishments are nowadays spread across the electronics industry placing pressure on the packaging technology to concurrently evolve and contribute to accomplishing the same goals at the PCB level.*

## 2. Electronic Packaging Overview

Electronics packaging is a critical aspect of designing and manufacturing electronic devices. It involves both the physical enclosure of the electronic components, and the methods used to protect and connect them. Table 5 presents the key areas in electronic packaging.

**Table 5. Key areas involved in electronics packaging**

| Electronic Packaging Area       | Description                                                                                                                                                                                                                                |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Enclosures</b>               | These are the outer casings that protect electronic devices from physical damage, environmental factors, and electrical interference. Materials used can range from plastics and metals to specialized composites.                         |

| <b>Thermal Management</b>       | Electronics often generate heat, so packaging needs to manage and dissipate this heat effectively. Heat sinks, thermal pads, and fans are common components used to ensure that electronic devices operate within safe temperature ranges. |

| <b>Mechanical Protection</b>    | Packaging provides mechanical protection to delicate electronic components from shocks, vibrations, and other physical stresses during transportation and operation.                                                                       |

| <b>Electrical Connections</b>   | This includes connectors, soldering, and other methods used to establish electrical connections between different components of a device. Good design ensures reliable and efficient performance.                                          |

| <b>Signal Integrity</b>         | Proper packaging helps maintain the integrity of electrical signals by minimizing interference and cross-talk between components.                                                                                                          |

| <b>Environmental Protection</b> | Packaging often includes measures to protect components from moisture, dust, and other environmental contaminants. This can involve sealing techniques, conformal coatings, and the use of protective enclosures.                          |

| <b>Design and Aesthetics</b>    | The design of the packaging can also affect the user experience. It needs to be both functional and visually appealing, considering factors like ergonomics and branding.                                                                  |

| <b>Sustainability</b>           | There is increasing emphasis on using recyclable and environmentally friendly materials in electronics packaging to reduce waste and environmental impact.                                                                                 |

| <b>Compliance and Safety</b>    | Packaging must adhere to various industry standards and regulations related to safety, electromagnetic compatibility (EMC), and other factors.                                                                                             |

Figure 4. Early Wire Bond Packaging Solutions

### Summary of Packaging Technologies

Semiconductor packaging technologies have evolved significantly to meet the increasing demands for performance, miniaturization, and functionality in electronic devices. Table 6 presents a comprehensive list of major semiconductor packaging technologies and their main features.

**Table 6. Major semiconductor packaging technologies and their main features**

| Packaging Technology                                                                                                                                                                                                                                                | Main Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Dual In-line Package Ceramic Packages</b><br>A traditional package with two parallel rows of pins extending from the sides. Uses ceramic materials as the packaging substrate.  | <ul style="list-style-type: none"> <li>High Thermal Conductivity: Good for high-power and high-frequency applications.</li> <li>High Reliability: Provides excellent protection against environmental factors.</li> <li>Cost: Generally, more expensive than organic packages.</li> <li>Easy to Handle: Simple to insert and remove from sockets.</li> <li>Through-Hole Mounting: Pins go through holes in the PCB.</li> <li>Low Pin Count: Generally used for packages with a lower number of pins.</li> </ul> |

| <b>Surface-Mount Device (SMD)</b><br>Components mounted directly onto the surface of the PCB without through-hole pins.  <p>Surface Mount Leaded Components</p>                    | <ul style="list-style-type: none"> <li>Compact Design: Reduces PCB space compared to through-hole designs.</li> <li>Automated Assembly: Suitable for high-volume manufacturing.</li> <li>Improved Performance: Shorter signal paths and better electrical performance.</li> </ul>                                                                                                                                                                                                                               |

| <b>Quad Flat Package (QFP)</b><br>A package with leads extending from all four sides.                                                                                            | <ul style="list-style-type: none"> <li>High Pin Count: Suitable for ICs with a high number of connections.</li> <li>Surface-Mount Technology: Mounts directly onto the PCB.</li> <li>Varied Pitch Sizes: Available in different lead pitches (distances between leads).</li> </ul>                                                                                                                                                                                                                              |

| <b>Ball Grid Array</b><br>A package where the IC is connected to the PCB via an array of solder balls. (BGA)                                                                     | <ul style="list-style-type: none"> <li>High Pin Density: Accommodates a large number of connections in a compact area.</li> <li>Improved Performance: Better electrical performance and thermal management.</li> <li>Reflow Soldering: Solder balls are melted and solidified during reflow soldering.</li> </ul>                                                                                                                                                                                               |

| <b>Chip-on-Board (COB)</b><br>Description: ICs are directly attached to the PCB, usually with wire bonding.                                                                      | <ul style="list-style-type: none"> <li>Cost-Effective: Reduces the need for a separate package.</li> <li>Compact Design: Suitable for applications with space constraints.</li> <li>Direct Electrical Connections: Wires connect the die directly to the PCB.</li> </ul>                                                                                                                                                                                                                                        |

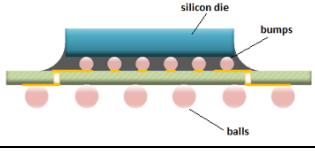

| <b>Flip-Chip (FC)</b><br>The IC die is flipped over and mounted directly onto the substrate with solder bumps.                                                                                                                                                      | <ul style="list-style-type: none"> <li>High Performance: Shorter electrical paths improve performance.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| Packaging Technology                                                                                                                                                                                                                                                                                                                 | Main Features                                                                                                                                                                                                                                                                                      |