INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

# INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS<sup>TM</sup>

# 2023 Update

# Systems and Architectures

THE IRDS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

© 2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

The IEEE emblem is a trademark owned by the IEEE.

"IEEE", the IEEE logo, and other IEEE logos and titles (IRDS<sup>TM</sup>, IEEE 802.11<sup>TM</sup>, IEEE P1785<sup>TM</sup>, IEEE P287<sup>TM</sup>, IEEE P1770<sup>TM</sup>, IEEE P149<sup>TM</sup>, IEEE 1720<sup>TM</sup>, etc.) are registered trademarks or service marks of The Institute of Electrical and Electronics Engineers, Incorporated. All other products, company names or other marks appearing on these sites are the trademarks of their respective owners. Nothing contained in these sites should be construed as granting, by implication, estoppel, or otherwise, any license or right to use any trademark displayed on these sites without prior written permission of IEEE or other trademark owners.

## **Table of Contents**

| Ack | knowle | dgments          |                                                                           | V  |

|-----|--------|------------------|---------------------------------------------------------------------------|----|

| 1.  | Introc | luction          |                                                                           | 1  |

|     | 1.1.   | Summa            | ary and Key Points                                                        | 1  |

|     | 1.2.   | Approa           | ch to Highlighting Key Challenges                                         | 1  |

|     | 1.3.   |                  | Teams                                                                     |    |

| 2.  | Drive  |                  |                                                                           |    |

|     | 2.1.   |                  | al and Application pull                                                   |    |

|     | 2.1.   | 2.1.1.           | The Transition from Decision-Support to Decision-Making Systems           |    |

|     |        | 2.1.2.           | Focusing upon Ensuring Supply Chain Anti-fragility                        |    |

|     |        | 2.1.3.           | Evolution of Edge to Cloud Platforms towards Pervasive Data Analytics     |    |

|     | 2.2.   | Emergi           | ng Trends                                                                 | 6  |

|     |        | 2.2.1.           | Cambrian Explosion of Architectures                                       | 8  |

|     |        | 2.2.2.           | From Programming to Training and Inference                                |    |

|     |        | 2.2.3.           | From One Physics to Many                                                  |    |

|     |        | 2.2.4.           | From Data Centers to Data Everywhere                                      |    |

|     |        | 2.2.5.           | From Imperative to Declarative                                            |    |

|     |        | 2.2.6.<br>2.2.7. | From Scarce Memory to Abundance                                           |    |

|     |        |                  | From Hindsight to Foresight                                               |    |

|     |        | 2.2.8.<br>2.2.9. | From General Purpose to Built-for-Purpose<br>From Proprietary to Open     |    |

|     |        | 2.2.9.           | From Central Authority to Distributed Systems                             |    |

|     | 2.3.   |                  | ctural Trends                                                             |    |

|     | 2.5.   | 2.3.1.           | Internet-of-things and Cyber-physical Systems                             |    |

|     |        | 2.3.2.           | Convergence                                                               |    |

|     |        | 2.3.3.           | Edge to Cloud Service Meshes                                              |    |

| 3.  | Syste  | m categ          | ory—Cloud                                                                 | 13 |

|     | 3.1.   | 0                | Drivers                                                                   |    |

|     | 3.2.   |                  | nges and Opportunities                                                    |    |

|     | 3.3.   |                  | Envelope Considerations                                                   |    |

|     | 5.5.   | 3.3.1.           | Trends of Processors for High-End systems                                 |    |

|     |        | 3.3.2.           | Acceleration Technology                                                   |    |

|     | 3.4.   | Metrics          | for cloud processors                                                      |    |

| 4.  |        |                  | jory—Personal Augmentation                                                |    |

|     | 4.1.   | -                | Drivers                                                                   |    |

|     | 4.2.   |                  | nges and Opportunities                                                    |    |

|     |        |                  | •                                                                         |    |

|     | 4.3.   | 4.3.1.           | Envelope Considerations<br>Trends of Processors for Personal Augmentation |    |

|     | 4.4.   | Metrics          | for Personal Augmentation Processors                                      |    |

| 5.  | Syste  | m Categ          | jory—Internet-of-Things Edge (IoTe) Devices                               | 23 |

|     | 5.1.   |                  | Drivers                                                                   |    |

|     | 5.2.   |                  | nges and Opportunities                                                    |    |

|     | 5.3.   |                  | Envelope Considerations                                                   |    |

|     |        | 5.3.1.           | Trends of Processors for Internet-of-Things edge (IoTe)                   | 23 |

| 6. | Syste | em Category—Cyber-physical Systems                                    | 26       |

|----|-------|-----------------------------------------------------------------------|----------|

|    | 6.1.  | Market Drivers                                                        | 26       |

|    | 6.2.  | Challenges and Opportunities                                          | 26       |

|    | 6.3.  | Design Envelope Considerations<br>6.3.1. Trends of Processors for CPS | 26<br>27 |

|    |       | 6.3.2. CPS Devices                                                    |          |

|    | 6.4.  | Metrics for CPS Processors                                            | 28       |

| 7. | Concl | lusions, Recommendations and Future Plans                             | 29       |

| 8. | Refer | rences                                                                | 33       |

### List of Tables

| Table SA-1.  | Application Benchmark/Systems and Architecture Cross Matrix         | 3       |

|--------------|---------------------------------------------------------------------|---------|

| Table SA-2.  | Technology Trends of Latency Sensitive Processors                   | 16      |

| Table SA-3.  | Technology Trends of Throughput Oriented Processors                 | 17      |

| Table SA-4.  | Performance Trends in High-End GPUs with High Bandwidth Memory (HBM | /I) .18 |

| Table SA-5.  | Trends for FPGAs in High Performance Applications                   | 18      |

| Table SA-6.  | System Category Cloud—Key Processor Metrics                         | 19      |

| Table SA-7.  | Trends of SoC processors for Personal Augmentation Devices          | 21      |

| Table SA-8.  | Personal Augmentation Technology Requirements                       | 22      |

| Table SA-9.  | Internet-of-things Edge Technology Requirements                     | 25      |

| Table SA-10. | Trends of MCU processors for ADAS                                   | 27      |

| Table SA-11. | Cyber-physical Systems Technology Requirements                      | 28      |

## List of Figures

| Figure SA-1. | SWaP Design Centers across Infrastructure System Categories 6 | 3 |

|--------------|---------------------------------------------------------------|---|

| Figure SA-2. | Cloud Energy Usage based upon BIT Transition Cost14           | 1 |

### ACKNOWLEDGMENTS

Roadmaps are inherently a team effort. Our Systems and Architectures team would like to thank our colleagues on the other teams for their information, input, and suggestions. We would also like to extend our appreciation to the IRDS leadership team for their insight and guidance. I would like to wholeheartedly thank our Systems and Architectures team members for their diligence and creativity: Kirk Bresniker, Terry Cox, Dr. Yoshi Hayashi, Ian O'Connor, Hiroyuki Kondo, Masaaki Kondo, Tsutomu Matsushita, Nobuhiko Nakano, Takura Norikatsu, Kentaro Sano, Mitsuhisa Sato, Toru Shimizu, Satoshi Takagi, Yoshiki Yamaguchi.

IRDS Systems and Architecture Chairs Kirk Bresniker and Stephen Dukes

# SYSTEMS AND ARCHITECTURES

### **1. INTRODUCTION**

The Systems and Architectures section of the roadmap serves as a bridge between application benchmarks and component technologies. The systems analyzed in this section cover a broad range of applications of computing, electronics, and photonics. In this chapter, we identify key challenges and technology requirements by observing the patterns in play in the systems and architectures anticipated during the period under study.

To make a complex domain more approachable, we have presented information as a series snapshots taken from specific viewpoints, upon individual areas of concern. We start by looking at drivers for change and imminent trends across the industry. We consider how societal change and customer demand reveal new high value problems (Application Pull) and then look at how new architectural capabilities create emerging trends (Technology Push).

In the second section, we present a series of application-specific views, each considering a different class of system, highlighting the goals and challenges specific to each area. We have resisted the urge to seek to classify the industry into what would be an impractically over-simplified hierarchy and instead urge the reader to consider each category as an isolated narrative intended to highlight the concerns that exist within a specified application area. In practical terms, there is considerable overlap between each class of system discussed and it will become immediately apparent that challenges illustrated in one section can be seen to repeat at different scales across many of the systems considered. Our intent is to illustrate important challenges in context, in the simplest form possible, for ease of communication.

A note on the 2023 edition: this is a minor edition update. Given the technology inflection points being driven from the top down by pervasive application of discriminative and generative AI and from the bottom up by heterogeneous integration we are focusing on the major update due in 2024. For a summary of the areas of investigation for the major update see section 7.

#### **1.1. SUMMARY AND KEY POINTS**

- All types of systems considered are intrinsically linked by the **lifecycle of artificial intelligence (AI)** and this has implications for the optimization of any given type.

- Building **anti-fragile supply chains** is critical for sustainable growth in the industry. This is a fractal pattern that impacts all points in the supply chain at all scales.

- We expect **artificial intelligence** and **augmented reality** to continue to act as important drivers for the growth of all four system areas, especially in supporting the **massive underlying data analytic flows**.

- Our ability to optimize supply chain capabilities with AI are constrained by our current commercial models with respect to training data. A **conceptual shift** is necessary to move to the next level.

- Internet-of-Things (IoT) and cyber-physical systems (CPS) both generate vast quantities of data that will accelerate the growth of big data and create a continuum of **edge to cloud** systems.

- Advanced packaging is a key technology for enabling architectural diversity. Chiplets on 2.5D substrates, the wide variety of 3D technologies, and wafer-scale integration using fine pitch lithography can provide significantly increased local bandwidth.

- When coupled with photonics technology, fabric attached memory (both DRAM-based and non-volatile), and the recent emergence of the reduced instruction set computer instruction set architecture (RISC-V ISA) and other open source hardware initiatives, future architectures could become both more flexible and specialized, opening up new **architectural dimensions of innovation**. However, managing this **extreme heterogeneity** will present difficult application development and system software challenges.

- As data grows disproportionately at the edge, computation will follow it, with increasingly demanding workloads in increasingly challenging space, weight, power, performance and cost envelopes creating opportunity for non-conventional architectures and approaches including those tailored to harvested energy.

#### **1.2. APPROACH TO HIGHLIGHTING KEY CHALLENGES**

To best understand the challenges currently presenting, we categorize systems by *design envelope*, allowing us to consider the aspects of Space, Weight, and Power (SWaP) as well as performance demanded in each category.

In subsequent discussions, we consider the following *four different categories of systems*:

- 1. Internet-of-things edge (IoTe) devices provide sensing/actuation, computation, security, storage, and wireless communication. They are connected to physical systems and operate in wireless networks to gather, analyze, and react to events in the physical world. These are ubiquitous-scale objects that pervade the environment.

- 2. Cyber-physical systems (CPS) provide real-time control for physical plants. Vehicles and industrial systems are examples of CPS. These can be considered 'human analog'-scale objects that fill niches previously covered by people.

- 3. Personal Augmentation devices such as smartphones, wearables and AR devices provide communication, interactive computation, storage, and security. For many people, smartphones provide their primary or only computing system. These are typically human-scale objects intended to augment the capabilities of an individual. In prior revisions of this chapter, we tracked this category as Mobile Devices, but this is no longer sufficient to capture the increasing diversity in this category.

- 4. Cloud systems power data centers to perform transactions, provide multimedia, and analyze data. Cloud systems represent a trend towards a synthesis of design principles and methodologies taken from traditional enterprise, high performance scientific, and web native compute. Increasingly these systems are utilizing artificial intelligence to continue to improve operational efficiency, becoming CPS in their own right. These are macro-scale, distributed systems.

Given the wide range of systems—ranging from self-powered monolithic very large-scale integration (VLSI) devices to industrial park-sized data centers—each has its own set of market drivers, challenges and opportunities, power and thermal considerations, technology targets and metrics as described in Sections 3 through 6.

With respect to the previously defined categories, we identify the constraints of power consumption for associated processors and devices as follows:

- 1. Processors with less than 10mW power consumption: processors in this category target sensing devices in IoTe systems.

- 2. Processors with 100mW-10mW power consumption: processors in this category are mainly used for embedded systems, aiming for high performance with lower than 100mW power budget.

- 3. Processor with 10W-100mW power consumption: processors in this category do not require cooling systems like heat sinks or cooling fans, and are used for personal augmentation and ADAS (Advanced Driver Assistance Systems) applications.

- 4. Processors for high-end systems including cloud, servers and supercomputers: since there are many variations in cooling methods such as water cooling, power supply, and installation conditions, mainly in data centers, the constraints of power consumptions are different. The constraint for power consumption of systems depends on the cooling technologies and the total power supply of the facilities. For example, in the cloud, as long as the power efficiency of processors is kept good enough such that the processors can be cooled, there is no power limitation per chip. Therefore, the main criterion is the power efficiency of processors.

For the modern advanced systems, the acceleration technologies such as graphics processing unit (GPU) and field programmable gate array (FPGA) are indispensable for high performance and efficiency. While this adds burden to the software environment, the SWaP efficiency they yield is increasingly required for viable business models balancing operational cost versus development and maintenance costs.

Increasingly, these four categories of systems are being combined into entire edge-to-cloud, large scale, and intelligent social infrastructure systems of complex interlocked information lifecycles. Each is continuing to demand ever greater capacity in diminishing space, weight and power envelopes, giving economic motivation to gaining as much as we can from conventional approaches as well as even greater potential for novel approaches.

Although we are considering each of these categories independently, it is important to understand that the process of building AI solutions is a super-system that spans all the above types. Typically, data will be collected from personal augmentation and IoT devices at the edge and aggregated in the Cloud in order to support the efficient training of machine learning models at scale. These models are then packaged and deployed back to cyber-physical edge systems that can perform real time inferencing upon live data from the original personal augmentation and IoT devices. Thus we must consider the impact of both operational and training phases of these systems as they become the dominant architecture in future.

#### **1.3. CROSS TEAMS**

The Systems and Architectures roadmap team interacts with several other roadmap focus teams. The Application Benchmarking team provides application data that informs our system architecture analysis. The Outside System Connectivity team provides insight into the ongoing interplay of photonics and fabrics, which at the rack, aisle, and data center scale is blurring the lines between compute, storage, networking infrastructure. More Moore and Beyond CMOS provide the novel computation, memory, and communications devices which are being increasingly required at the extremes of edge and exascale.

|                            | Cloud | юТе | CPS | ΡΑ |

|----------------------------|-------|-----|-----|----|

| Big Data Analytics         | Y     | Y   | Y   | Y  |

| Artificial Intelligence    | Y     | Y   | Y   | Y  |

| Discrete Event Simulation  | Y     |     |     |    |

| Physical System Simulation | Y     | Y   | Y   |    |

| Optimization               | Y`    |     | Y   |    |

| Graphics/AR/VR             | Y     |     |     | Y  |

| Cryptographic Codes        | Y     | Y   | Y   | Y  |

Table SA-1.

Application Benchmark/Systems and Architecture Cross Matrix

### 2. DRIVERS

In this section, we discuss both Societal and Application Pull (i.e., changing demands and applications which define the targets that systems and architectures should fulfill) as well as Architectural and Technology Push (i.e., how the underlying technologies - from components to software stacks - are opening up new opportunities for growth).

#### 2.1. SOCIETAL AND APPLICATION PULL

#### 2.1.1. THE TRANSITION FROM DECISION-SUPPORT TO DECISION-MAKING SYSTEMS

Historically, systems architectures have always been built upon the presupposition that many, independent sources of record provide information to support human decision-makers who integrate this information and execute appropriate actions. It is implicitly assumed that people are at the center of the architecture, reconciling disparate and often contradictory information.

There are, however, fundamental limits to scale for people-centric organizations, with most demonstrating an S-curve for growth. Nonetheless, at the forefront of the New Economy, a growing number of enterprises are transitioning to a business model where machine learning is leveraged to replace people in the decision-making process, facilitating more reliable replication and execution of business strategy, at much larger scale.

Given the significant commercial advantages conferred by this approach, it is anticipated that the majority of businesses will be forced to adopt this strategy to remain competitive. As a result, we must expect a fundamental conceptual shift in systems architectures, as demand moves from an annual or quarterly cadence of decision-support data that is human-readable, to a real-time stream of moment-by-moment information intended to be acted upon by AI models.

Societally, this is expected to introduce disruption larger in scale than the industrial revolution, with almost all industries, roles and products being transformed through new ways of looking at existing problems with these enabling technologies. Whilst this is likely to be extremely positive for the semiconductor industry in general, we should be mindful not to see the future as 'more of the same, but faster' and should anticipate a 'Cambrian explosion' of novel applications and products, some of which should be expected to disrupt the industry itself.

#### 2.1.2. FOCUSING UPON ENSURING SUPPLY CHAIN ANTI-FRAGILITY<sup>1</sup>

In previous editions of the roadmap, we have focused upon aspects of reliability, availability, serviceability and security of individual systems, in line with the vertically integrated and turnkey nature of many solutions within the industry. Current

<sup>&</sup>lt;sup>1</sup> While fragile systems are harmed by volatility and dependable systems are tolerant of volatility, an "anti-fragile" system becomes stronger in the face of volatility. As external factors in the near future continue to increase volatility, anti-fragility is necessary in order to thrive in this context.

thinking in this space has evolved rapidly, however, and it is important to recognize the intrinsically fractal nature of the challenges found in this problem domain. Recent events have placed our attention firmly upon our position in the global supply chain and helped to reveal that no matter at what scale you look, you find the same set of patterns repeating at each level.

As a result, it has become obvious that the aspects of reliability, availability, serviceability and security should be considered as holistic components of maintaining the supply chain. Rather than approaching the problem from a system component level, we should instead be mindful of how a security vulnerability in a dependency relied upon by one of our suppliers can be utilized by attackers to create reliability issues in our systems that in turn facilitate availability problems for our customers in ways that can be leveraged into adversarial attacks on a global scale.

Manipulation of the global supply chain has become a valid target for both political and financial gain in the early 21<sup>st</sup> Century. On top of this, we anticipate increasing volatility as a result of climate change, geo-political unrest and the disruption of the move to AI upon modern society. Success under these conditions requires not just a robust and resilient supply chain position, but one that should be strengthened by volatility rather than merely resistant to it.

It is important, therefore, that we view this problem as a network of systems of systems, somewhat akin to the way that the protocols underpinning the Internet were designed to automatically route around disruption and automatically recover from transient faults.

Basic tools still include the use of increasingly higher levels of cryptographic protection, authentication, and attestation. While these techniques are well established over communications networks, they are now being brought down to the level of component-to-component communications. In addition to cryptographic protection of data both at rest and in flight, which requires both cipher engines as well as key management, this zero-trust model will require authentication exchanges between components prior to utilization. Authentication will itself require management of certificates and may eventually need to be linked back to a physically uncloneable function (PUF) [2] of a silicon device itself. This will place an added demand on fabs to not only manufacture the components but to also provide the provenance (traceability) of the components so that they can be authenticated prior to every use. Increasingly, the ability to detect a massive, distributed advanced persistent threat will likely require artificial intelligence to proactively detect anomalous behaviors across the complex edge-to-cloud infrastructure, but that in turn will require increases in computational efficiency and data analytics to establish the base lines and chains of evidence. Cybersecurity and AI are co-dependent for continued advancement.

Beyond this, however, is a broader commercial problem that must be addressed if we are to fully realize the benefits of AI within the industry. The wider goals of supply chain optimization depend upon accurate and reliable machine learning models that require large volumes of data for training. In the context of the supply chain, this data is owned by many stakeholders and may contain detail that reveals proprietary IP or commercial liability. As a result, there is an inherent bias against data sharing at a level that can support the necessary modeling.

To move beyond this blocker, it will be necessary to find commercially acceptable forms of data sharing that permit improvements in supply chain whilst protecting business interests and confidential IP to the highest standards.

#### 2.1.3. EVOLUTION OF EDGE TO CLOUD PLATFORMS TOWARDS PERVASIVE DATA ANALYTICS

All four of the following application areas are in general use: 1) Internet-of-Things networks perform important services in a range of applications; 2) cyber-physical systems provide essential services; 3) personal augmentation devices number in the billions worldwide—regardless of whether they are operated privately or for public consumption; and 4) cloud systems are engendering new programming languages and methodologies and cloud-native computing.

These systems do not exist in isolation. Personal augmentation devices, IoT edge devices, and cyber-physical systems all provide data that is analyzed by cloud systems. Many complex systems exhibit characteristics of both IoT and CPS. Certain aspects of data centers and cloud systems—power management and thermal management, for example—make use of cyber-physical and IoT techniques. Figure SA-1 presents these associations across nine SWaP design envelopes ranging from embedded to exascale high-performance computing (HPC) data centers and how the IoT edge, CPS, and Data center categories overlap. A next-generation social infrastructure solution, such as intelligent mobility or AR/VR augmented gaming will position the fourth category, personal augmentation devices, to interact with all of these design envelopes to deliver a complete solution.

The volume of data generated by IoT and cyber-physical systems is staggering. The sensor fusion platforms of a fleet of 1000 conventional circa 2018 connected ADAS vehicles generate four petabytes per day of data from their onboard sensors; that volume of data is equal to the total data volume handled at that time by Facebook (now Meta). While today the vast majority of in-vehicle data is discarded after it has been analyzed to provide immediate operational and safety benefits, efficiency breakthroughs allowing *in situ* analysis of raw data in IoT and CPS systems could provide extremely disruptive economic potential. What may evolve is the edge-to-cloud platform where today's hub-and-spoke model is replaced by complex and

dynamic topologies where cloud as-a-service consumption models are extended out from the data center towards successively smaller edge device meshes. As increasingly sophisticated computation infrastructure is distributed towards edge devices, a new class of latency-sensitive distributed massive data analytic applications could emerge, such as: intelligent mobility systems, 5G and successive communications networks and advanced AR/VR gaming applications are all examples of application classes where millisecond or microsecond latencies on complex data analytic and data synthesis workloads may demand several tiers of computational capacity trading off space, weight, power and performance against latency.

What admits data into economic activity is an information lifecycle — acquisition, assurance, analysis, insight and action—in which the analysis allows for timely action and for which the costs of analysis are outweighed by the benefits of action. Timeliness is the most important constraint, followed by the per cycle costs of analysis, yielding a time limited return on the investment of infrastructure and energy. At every scale of the design envelope from embedded IoT devices to exascale data centers, the numerator and denominator of this time-limited return on investment (ROI) can be affected by adoption of novel computational, memory and communication approaches from both the "More Moore" and "Beyond CMOS" roadmaps.

| DESIGN<br>ENVELOPE         | SYS  | TEM C                         | ATEG | ORY           | INTEGRATED TECHNOLOGIES                                                                                                                                                                                                                                                         |

|----------------------------|------|-------------------------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Beacon &<br>Sensor Nodes   |      |                               |      |               | Trusted data sources<br>2.5D/3D integration of sensors, memory, accelerators, computation, and comms<br>Energy Harvesting with inducted power boost modes<br>SRoT/Blockchain trust mechanisms                                                                                   |

| Access Point               | _    | Perso                         |      |               | Unified 5G/Wi-Fi access point for IoT sensor network<br>Identity, Activity, Locality triangulation<br>ML/AI augmented operation                                                                                                                                                 |

| Aggregation<br>Point       | loTe | Personal Augmentation Devices |      |               | Robust environmentals<br>Edge local secure hosting of containerized workloads<br>Static composition<br>Smallest IT/OT (Information technology / Operational Technology) Blended Platform                                                                                        |

| Edge Hardened              |      | ation Dev                     | CPS  |               | Robust environmentals<br>Legacy PX/AXe plus next gen modular FF<br>Static composition<br>Robust IT/OT Blended Platform target at several capacity points                                                                                                                        |

| Personal Sensor<br>Network |      | ices                          | S    |               | Sensor Fusion Platforms for ADAS, SCM, SNS, etc.<br>Gaming applications with milisecond or microsecond latencies<br>Computation for security satisfying frameworks like GDPR                                                                                                    |

| User Equipment             |      |                               |      |               | 5G/6G Smartphones<br>Wearables with ultra-low power consumption<br>Graphics/AR/VR devices as human analog-scale objects                                                                                                                                                         |

| Single System<br>Flex      |      |                               |      |               | OPC/Rack/Tower systems with next gen modular FF option bays and<br>electrical/optical memory fabric (Gen-Z/CXL) expansion<br>Static fabric configurations between reboots<br>Low cost point-to-point expansion                                                                  |

| Enclosure<br>Composable    |      |                               |      |               | Blade Enclosure augmented with next gen modular FF and memory fabric at the enclosure and rack level<br>Enclosure level switching of fabrics<br>Static/Dynamic fabric configurations                                                                                            |

| Rack Scale                 |      |                               |      | Cloud Systems | Dense next gen modular FF enclosures with integrated switching<br>Large Scale memory fabric enclosure as endpoint<br>Dynamic fabric configuration<br>Dematertialized and legacy free<br>Design for Flex Capacity, Co-Lo, aaS Consumption models<br>Containers on memory fabrics |

| Aisle/Pod<br>Modular       |      |                               |      | ystems        | Dense next gen modular FF enclosures with integrated switching<br>ToR switch<br>Dynamic fabric configuration<br>Dematertialized and legacy free<br>Design for Flex Capacity, Co-Lo, aaS Consumption models<br>Petascale HPC and Petascale Enterprise in-memory DB/Analytics     |

| Exascale HPC               |      |                               |      |               | DC scale memory-semantic fabric over photonics<br>All liquid/conduction cooling environmentals<br>Aisle/Pod modular for I/O nodes<br>2.5D/3D integrated CPU/GPU/Memory modules                                                                                                  |

Figure SA-1. SWaP Design Centers across Infrastructure System Categories

#### 2.2. EMERGING TRENDS

Artificial intelligence [3] continues to be a primary driver for the demand for growth in capabilities. Increasing levels of AIdriven computation are being provisioned in the cloud, but many advantages exist to performing decision-making tasks in real time at the edge, so we expect personal augmentation systems, IoT edge devices, and cyber-physical systems to all include significant AI components.

In all cases, this move towards pervasive AI creates new demands on data analytics, both in the training of AI/machine learning (ML) models and in the value of inference of those models on novel data sources. For time critical inferencing, this will mean the desire to host increasingly complex models in decreasingly small SWaP footprints, including in energy harvested environments. For use cases in which the subject matter, such as natural language processing, is under continuous evolution, the

models will need to be continually improved, which at a minimum creates the need for secure over the air updates but also may require distributed attestation and training when data sets are prevented either by law or by economics from being centralized for continuous re-training. Since models are continuously derived from data, the provenance and security of the data flowing into these continuous integration and deployment regimes becomes paramount and must be reflected in security and attestation features down to the lowest level devices.

We still expect AR/VR to emerge as an important application area, however there are significant challenges in developing suitably compact interface devices that will begin to drive social acceptance of this degree of obvious augmentation in social spaces. A primary challenge in this domain remains the need to synthesize data streams captured locally with geographically and contextually related live and pre-distributed data streams, within the perceptual limitations of the users, which places speed-of-light limitations for low latency computational turnaround. In the meantime, a core driver for personal augmentation systems is instrumentation, with health monitoring, safety alerting and sensory enhancement all being significant value added features to devices in this category.

The combination of low cost AR interfaces and low latency 5/6G networking, along with the mass exposure to remote working triggered by the pandemic open the path to many opportunities in telepresence. It is expected that advances in haptics, proprioception, and perhaps olfactory and gustatory transducers will be necessary to support this in comfort.

Even as IoT and CPS both continue their massive build outs, security and data privacy concerns remain a significant problem.

While we continue to describe IoT, CPS and Cloud as distinct classes, edge-to-cloud is emerging as a continuum, where a clear cycle of 'collecting data at the edge, moving it to the cloud for training, then exporting models to the edge for low latency inferencing' is becoming visible. Industry analysts have predicted that by 2025 as much as 75% of enterprise generated data will never be housed in a traditional data center—public or private. That data and the computational platforms that will provide access to and analysis of that data will be increasingly geographically dispersed into communications, power, transportation and building systems. These systems will host both data and computational resources proximal to that data, all of which will be consumable on demand, however this introduces significant challenges with respect to regulatory compliance. Security of both the data at rest in edge systems and the access to it will require both cryptographic protections as well as end-to-end zero trust attestation that will be continuous from edge to cloud. There are emerging conflicts appearing between regional data protection and AI regulations that risk turning some regions into 'no-go zones' for CPS systems due to the impossibility of complying with proposed regulation. It is likely that we will see a gradual transition from current 'with-the-sun' Cloud based workloads to much finer grained distributed, in-network computing, which will in turn introduce a broad range of new commercial and regulatory challenges.

The radius of effective communication of data has become an increasing problem for Cloud and HPC systems. Modern datadriven applications must operate on huge datasets that cannot be held in traditional types of memories, nor be addressed directly by conventional microprocessors. Data access times to block storage can be orders of magnitude longer than access to limited, high speed, local storage, so programmers must use more sophisticated programming techniques to manage delay — techniques that are often rendered useless by algorithms that do not have predictable locality, such as graph analytics on time varying graphs. The move to a chiplet based approach to integration of memory and I/O complexes into massive systems on chips (SoCs) increases the capacity of low latency storage but as a result also relegates application specific accelerators to the block mode, high-latency off-chip regime, limiting the scalability of external acceleration.

As the number of cores available within a package continues to increase, this class of problem expands into an ever wider application space, exposing a fundamental challenge for software developers who continue to have difficulty making the transition from classical, single-threaded processing to techniques that push the limitations defined in Amdahl's Law. AI is likely to be the dominant driver for demand for new devices as conventional developers struggle to conceptualize the structures and architectures necessary to utilize the full performance of modern, conventional processors.

The complex integration of cache, memory, and I/O blocks alongside the high core count in the current generation of processors continues to reveal the specter of multiple, advanced, persistent threat side-channel attacks which can be used to subvert the integrity of solutions.

For dense rack, aisle and data center scale systems, the convergence of open memory-semantic fabrics and photonics are reshaping the moderate latency regime. When end-to-end latencies are between 300ns and 500ns, software designers can take advantage of relatively straightforward memory resource utilization mechanisms. Memory-semantic fabrics allow for the promotion of accelerators to first-class participants alongside general-purpose cores, allowing each to scale independently. Photonics allows data center distances to be traversed for the same energy cost as board to board distances and offers much greater physical design freedom and immunity from radio frequency interference (RFI) and emissions. When coupled with a high-radix switch, photonics and memory-semantic fabrics could offer affordable exascale memories at the rack scale, memory latencies at the aisle scale and unified message passing at the data center scale and potentially beyond.

#### 2.2.1. CAMBRIAN EXPLOSION OF ARCHITECTURES

As we move from 2D to 3D, we face a new inflection point represented by the opportunity for an explosion of new architectures that exploit the potential of stacking combinations of processing, memory, acceleration and I/O in denser and more efficient forms. This makes it difficult to project many elements of the roadmap forwards as we move from a period of familiar 'general purpose computing' devices to a proliferation of exploration into new ways to address current challenges.

It is anticipated that there will be a period of searching for commercial advantage through the application of specialized architectures that offer niche benefits in specific market segments as a result of these new physical device capabilities and there is likely to be significant product differentiation before we loop around to a commercial situation where 'modular IP within devices' becomes as common as the current 'modular devices on board' model.

There are likely to be two predictable trends in this period of innovation, however. Challenges currently experienced at a data center and HPC level will migrate down to a SoC scale as the problem becomes one of moving sufficient data at low enough latencies to fully utilize the number of cores available within a given device. Since this approach is only viable for certain classes of conventional software problems, we will also see multiple approaches to optimizing AI architectures which are a workload that can potentially benefit from intrinsic parallelization without the limitations inherent when requiring humans to design massively multithreaded architectures.

#### 2.2.2. FROM PROGRAMMING TO TRAINING AND INFERENCE

This shift is driven by the combination of open source software frameworks and the rise of AI machine learning frameworks capable of the creation of very effective models based on statistical inference. Unsupervised learning techniques can trawl huge volumes of structured and unstructured data to find correlations independently of expert blind spots. Intelligence craves data and artificial intelligence is no exception.

This creates a shift in the economic potential, from those who create code to those who create the data – without whom those code stacks are not useful. This also challenges us because the utility of these AI systems is limited – not by the ingenuity of the human programmers, but rather by the degree to which we have engineered systems to admit as much data as possible into the training regime as our physics and legal and security systems will allow.

Practically, it is important to note that the creation of models represents only about 5% of the effort needed to commercialize an ML-based product — significant work is required to improve machine learning operations (MLOps) tooling and processes to cover all the challenges that exist in this emerging space, as detailed in the MLOps Roadmap [7].

#### 2.2.3. FROM ONE PHYSICS TO MANY

Through the first two eras (geometric and equivalent) of semiconductor scaling, there have been incredible advances in the highlevel aspects of computer science — algorithms, programming languages, storage and communications technologies. However, they were all fundamentally modulated by the CMOS transistor. Innovations were tested against the cost and performance improvements predicted by Moore's law, and if they did not have the expected exponential growth characteristics they were not admitted.

Even the obvious defects in security source to the conceptual basis of software models based on the 1960s threat landscapes failed to be fixed at the source because of the dominance of architectures with the tailwind of CMOS advances.

Now, as CMOS advancement transitions from equivalent scaling to 3D Power scaling, novel computational approaches are increasingly competitive. The work that might spring most quickly to mind, e.g. quantum computing, along with cryogenic computing, has emerged as a particular focus area. However, it is not the only one - other areas include novel switching technologies, such as:

- Faster, more efficient switches using carbon nanotubes or 2D materials in the switch channels;

- Bringing computing resources to where the data is stored to reduce communication overhead with In-memory computing;

- Using the rich and orthogonal properties of light to densify data representation as well as resonance and interference phenomena to implement complex mathematical operators in silicon photonic computing;

- Adiabatic and reversible computing that operate at the limits of thermodynamic information theory;

- Neuromorphic and brain-inspired computing that draw inspiration from biological systems but, much as with aerodynamics, use materials and energies not available to their biological analogs, and

- Networks of organic and inorganic materials whose behavior calculates desirable functions at SWaP breakthroughs; as systems created in our own image that are designed primarily to host intellect that offer computation as a byproduct of intelligence.

#### 2.2.4. FROM DATA CENTERS TO DATA EVERYWHERE

Today, 90% of information that the enterprise (public or private) cares about is housed in a data center. By its very name, it describes the actions that we have undertaken. In order for data to enter into economic activity, it must be centered, either because it was born there or it had to be transported there. But, with the advent of so many rich, high definition sensors housed in the ever proliferating number of personal augmentation devices, that ratio is expected to shift to as much as 75% of enterprise information will *never* being housed in a data center.

It is not that the data center footprint will shrink, although it will continue to coalesce into clouds (both public and private), but that data will grow exponentially and disproportionately at the edge, in distributed social infrastructure, in edge devices (personal, public, and private - in other words, in all things intelligent).

There are two forces that keep data at the edge—physics and law. The exponential growth of recorded data, which currently doubles every two years, means that even with the advent of 5G communications and massive communication backbones, there will never be enough bearer capacity to centralize all the data and even if there was, Einstein's limit of the speed of light means that, at even metropolitan distances, our fastest communications will fail to meet the demands of autonomous vehicles or 5G communications.

The second force is law. There is no global standard on privacy and the relation and responsibility of the individual to the larger society, which means that there will never be (at least in the foreseeable future) a single regulatory regime that spans the globe. Just like citizens and goods today, data needs to obey the imposition of boundaries. Will frameworks like GDPR<sup>2</sup> continue to offer the protections that they strive to, when the vast majority of data will never be in a data center, and when the very term data center will be an oxymoron?

The question to ask here is, "What will it take to admit as much data as possible into economic activity?" The first answer is to exploit the asymmetry of the query versus the data to be analyzed. Instead of moving the data to the compute, move the compute to the data. This requires us to understand where we position potentially shared computation resources in proximity to the data—in sensors, edge devices, distributed edge compute enclosures, autonomous vehicles. The second requirement to admit data to activity is security in the broadest sense—protection, trust, and control.

- Protection: robust and energy-efficient cryptography ensures that query and response are demonstrably safe and correct.

- Trust: provenance backed by secure supply chains, silicon roots of trust, and distributed ledger systems with low energy consensus functions ensures that every byte flowing into an enterprise can be audited.

- Control: meta-data embedded unforgeably in the data ensures down to the byte and the access cycle all stakeholders in a computation can have their rights verified and protected.

- Specific examples of these challenges are addressed in more detail in the Factory Integration chapter.

#### 2.2.5. FROM IMPERATIVE TO DECLARATIVE

Imperative control systems rely on the enumeration of conditionals and responses, i.e. the classic if-then-else diamonds of flowcharts. The problem with imperative control is that the systems that we are creating—social, technical and economic—are too complex to be enumerated. No matter how much time we spend, we never can catch the corner cases, there are always exceptions and that means we need to guard band. Consequently, this means overheads and the inefficient use of resources, whether it is compute resource allocation, spectrum allocation or transportation capacity.

Declarative management instead relies on systems that expose their operational state and control surfaces to goal seeking algorithms, such as reinforcement learning. Instead of enumerating all the "ifs" and "thens," we can set goals to be achieved and let the system strive to maximize those goals. This approach has the added benefit that it does not suffer from the human bias of presupposition of causality preventing us from finding correlations hiding in plain sight. A declarative system using unsupervised

<sup>&</sup>lt;sup>2</sup> General Data Protection Regulation

learning and autocorrelation could naively, blindly discover those correlations humans discount because it cannot presume it knows better.

#### 2.2.6. FROM SCARCE MEMORY TO ABUNDANCE

A decade after Alan Turing created the mathematical theory of computation, John von Neumann was realizing that theory as an operational feat of engineering in his 1946 outline of EDVAC<sup>3</sup>. What von Neumann noted then, and what has remained true, is that the fundamental limiter to computation is how reliably and cheaply the memory can be made that can keep up with computation.

Computation performance has always advanced faster than memory performance. But that is changing. As we enter the age of 3D power scaling, memory is advancing faster than computation. The regular rows and columns of memory; the inherent shared, redundant, and repairable structures of memory, and the low power dissipation of memory mean that it can grow in the Z axis in a way that may never be possible for the high power and random logic of computation.

With a structure of layers within a die, die within a module, and modules within a package, memories can scale. At that point, the switch to photonic communications can allow the scaling to continue at the enclosure, rack, aisle and data center scale. A second scalability of memory is scalability in energy. All of the novel memory technologies looking to replace the transistor memory, phase-change, resistive, spin torque, magnetic, all have a degree of persistence. They cost energy to write, they cost much less energy to read, but they cost no energy to maintain their contents. This is what can allow all of those zettabytes of data into unsupervised learning that we can now afford the energy to hold it all in memory. It also reintroduces a technology older than electronic computation—the lookup table.

The table of numerical functions used to be the constant companion of the scientist or engineer. Energy was expended to calculate numbers one time, to write those numbers one time, and then those costs could be amortized in perpetuity. From the 1970s onwards, it has been cheaper to recalculate a result than to remember and recall it. But with persistent memories applied to immensely complex calculations like machine learning routines, incredible volumes of information can be distilled into insights that can be taken to the most energy-starved environments like interplanetary space.

#### 2.2.7. FROM HINDSIGHT TO FORESIGHT

If we consider all of the information technology infrastructure of a Fortune 50 company, the alphabet soup of HR, CRM, ERP, GL systems, we will find a system of hindsight knowledge. That is because what represents the state function of the enterprise—the operational data of all of those systems—is spread over petabytes in thousands of relational databases connected by hundreds of thousands of asynchronous updates, and much of that data would be copies. In order to evaluate the state function of the enterprise, we need to go through a ritual of reconciliation. We need to "close the books", take a snapshot of all of those systems and painstakingly reconcile them. It is only then that a CEO/CFO executive leadership team can obtain a value of the state function of the enterprise, but it is at best days, most likely weeks old and represents a single moment in time, the instantaneous close of the period.

If, instead, we were able to hold all of that operational state in a unified memory, evolving as a time varying graph, then we can achieve insight. The system function of the enterprise can be evaluated instantaneously and continuously, which means that we can also take its derivatives with respect to time and understand velocity and acceleration, gradient and curl. Now decision makers can ask any ad hoc question and the enterprise can answer. We have extended the concept of a digital twin from its origins in physical systems management and extended it to economic systems management. But what is more, we can unleash unsupervised learning and anomaly detection tools to audit and analyze the data, looking for the telltale signs of fraud or inefficiency. But we can also extend the preventative maintenance concepts to this new economic model. While machine learning gives us powerful statistical inference tools to find in data the patterns we've seen before, techniques like graphical inference and belief propagation allow us to predict behaviors we haven't seen.

From hindsight ("what has been happening around here") we gain insight ("what is happening right now") and then foresight ("what most likely to happen next").

#### 2.2.8. FROM GENERAL PURPOSE TO BUILT-FOR-PURPOSE

"log2(X)\*24 Traditionally, that is how long a point innovation has had to survive in months. If one expects an advantage of "X" times the state of the art today, then the log base 2 is how many doublings it will take to match. The Moore's Law doubling period of 18~24 months has set the timeframe for innovation, especially when Dennard scaling was still available. Faster, cheaper to make and cheaper to use is a triple word score. Unfortunately since Dennard scaling ended 15 years ago the straightforward

<sup>&</sup>lt;sup>3</sup> Electronic Discrete Variable Automatic Computer

way to continue to reduce power and increase performance has been to make larger and larger die. We are at the point now of "dark silicon," which means that we can make more transistors than we can deliver power to. If all the circuits on a die were active, the heat could not be removed fast enough and the chip would fail. Add one more law, Rock's Law [4], the observation that each successive chip fab costs twice as much. "Moore – Dennard + Rock" is the recipe for consolidation at every level—the number of companies that can compete to the number of competitive architectures.

But during this transition period between equivalent scaling and 3D power scaling, may be a period when the tide will shift back to the economic value of novel accelerator design.

#### 2.2.9. FROM PROPRIETARY TO OPEN

The Open Source development and collaboration model has proven incredibly effective in software, not only in the complexity of systems that can be delivered, but also in the diversity of those who are enabled to participate. This creates the virtuous cycle where internationalization and localization occur as primary efforts coincident with innovation rather than after the fact, creating greater diversity of representation that again fuels greater inclusion in the economic and social benefits of innovation.

The same guiding principles of open source software development are being extended down the stack. As an example, Gen-Z [5] is a memory-semantic fabric driven by an industry consortium applicable to ever-increasing levels of integration, from embedded to exascale. It has been open for review by the open source software community during the entire draft period and lowers the barrier to innovation for novel computational, memory, and communications devices. Regardless of whether it maximizes the potential of conventional CMOS or enables new physics to accelerate a particularly onerous computation, lowering the barrier to innovation and breaking the cycle of improvement solely through consolidation is the antidote for today's technical monoculture.

RISC-V [6] is an Instruction Set Architecture with an open governance model which fully embraces the open source development model in that it is freely extensible and licensable. This is a unique new proposition which simultaneously allows for a sustained core software development model that also allows innovation and customization that can be realized in custom or programmable silicon. When coupled with the emerging capacity of multiple foundries of relatively competitive logic processes, this again enfranchises an ever increasing number of innovators everywhere.

#### 2.2.10. FROM CENTRAL AUTHORITY TO DISTRIBUTED SYSTEMS

Whether they are economic (cryptocurrency and public ledger), power (microgrids), or communications systems (mesh networks), distributed systems are more complex than centralized systems. But they are more sustainable, more available, more secure, and more equitable, which in turn makes them arguably more just.

#### **2.3. ARCHITECTURAL TRENDS**

#### 2.3.1. INTERNET-OF-THINGS AND CYBER-PHYSICAL SYSTEMS

This roadmap provides separate analysis of IoTe devices and cyber-physical systems. While both types of systems connect computing devices to the physical world, and there is some overlap in the usage of these terms, we believe that considering them separately in this roadmap gives readers greater insight into the evolution of such systems. We can contrast CPS and IoT systems in several ways:

- Cyber-physical systems perform real-time control—the core control functions operate automatically and without user intervention. IoT systems put more emphasis on sensing: they are also more likely to provide data summaries to humans who adjust system operation based on those summaries.

- Many cyber-physical systems are, at their core, based on wired networks, although wireless sensors may be used in these systems. IoT systems are often deployed over larger areas and make more extensive use of wireless connections.

- Cyber-physical systems tend to operate at higher sample rates than do IoT systems. We choose for convenience of discussion a boundary of 1 second between cyber-physical and IoT systems. IoT systems are often organized as event-driven systems that either react to sensor activations or transmit data only when analysis indicates that a signal is of significant interest.

#### 2.3.2. CONVERGENCE

The huge volume of data generated by IoT and cyber-physical systems means that within the next five years the majority and then the vast majority (as much as 75% by one estimate) will never reach traditional data centers. Even with the advent of increasing bandwidth from next generation 5G/WiFi6 wireless interconnects, data growth will out strip transmission capacity. Both transmission energy and costs as well as regulatory, security, and privacy burdens will keep data in edge devices. As edge systems become the majority of data resources, the desire to access them directly using the same cloud native APIs and continuous

integration / continuous deployment software development methodologies will increasingly drive security and performance features and their enabling components into CPS and IoTe devices. This represents a convergence of the traditional operational technology (OT) components and methodology with their information technology (IT) equivalents. This represents a security and attestation challenge as many OT technology standards have been developed with lightweight security and little to no attestation mechanisms.

For this reason and for the need to provide additional low latency computation, cloud-native enabled IT computational footprint ranging from rack scale down to ruggedized small single servers designed for extended environmental conditions will become gateways stitching together the OT and IT worlds.

#### 2.3.3. EDGE TO CLOUD SERVICE MESHES

Whether public or private, cloud systems today offer compute, storage, networking infrastructure deployable via Application Programming Interfaces (APIs), infrastructure as code. They also allow data and application resources to be deployed via APIs as well, usually up to the physical extent of an extended high-availability zone. The trend within a zone is for greater and greater levels of abstraction: data, applications, infrastructure are all abstracted as APIs and complex solutions are composed at scale and with high reliability and security without the developers having to understand, or have any access to, the lower level implementation details. This separation yields a degree of freedom on the cloud infrastructure designer to adapt novel technologies and to instrument the controls of these massive systems with AL/ML for operational efficiencies that human operators cannot achieve. However because of the lack of standards, compositing applications between zones of a single cloud provider, let alone across multiple providers, is extremely challenging. The disproportionate growth of data in edge systems coupled with the rise of low latency demanding applications such as AR/VR [3]may couple with the desire to compose solutions across the entire continuum of private to public cloud and edge to data center clouds in new constructs call service meshes. Service meshes may allow solution developers to balance latency, cost, reliability, security, privacy, availability and sustainability and re-introduce a counterforce to the consolidation of supply chain and lack of competition in current cloud data center providers. Key to service mesh construction is the adoption of ubiquitous zero trust endpoint security mechanisms rooted in physically uncloneable features in silicon and network independent name space resolution that can scale to a globally distributed edge to cloud ecosystem.

## 3. SYSTEM CATEGORY-CLOUD

The term *cloud* refers to the engineering of data center scale computing operations—compute, storage, networking engineered for scale and for continuous resource redeployment and reconfiguration via APIs. Whether they are operated publicly or privately, they offer an on-demand, as-a-service consumption model. While they had their origins in web services; media streaming, shopping and commerce; they are increasingly broadening their applications base to big data for social networking, recommendations, and other purposes; precision medicine; training of AI systems, and high-performance scientific computation for science and industry.

Cloud infrastructure has undergone several waves of optimization from its initial deployment of industry standard rack servers, storage and compute at data center scale. Starting with commercial off-the-shelf (COTS) systems, cloud infrastructure progressed to custom loading of standard systems to purpose-built at the motherboard level. Today's cloud-native compute, storage and networking infrastructure features bespoke processor designs, networking interface and switch ASICs, and workload specific accelerators via FPGAs or ASICs.

The traditional differences between high-performance scientific computation and the first generations of web-scale applications are diminishing. Scientific computation traditionally emphasizes numerical algorithms, whereas cloud applications, in contrast, emphasize streaming for multimedia and transactions for commerce and other database applications. Now, with AI/machine learning (ML) integrated into so many applications, the demand for accelerated floating point computation is more universal and all applications are being dominated by operational and capital costs of data movements at scale. In all cases, the general trend is also to utilize this as-a-service consumption model to foster independence of the user from not only a particular piece of hardware infrastructure but from one particular architectural approach. This is a critical enabler for introduction of novel computational approaches from either the "More Moore" or "Beyond CMOS" roadmaps.

#### **3.1. MARKET DRIVERS**

Market drivers for the cloud include direct services (multimedia, shopping, shared experience), big data and data analysis (social network analysis, AI, smart cities, smart industry, precision medicine). We note that while these applications have differed from traditional scientific computing applications that emphasize numerical methods, this distinction is becoming less important as data movement and storage costs come to dominate both application domains.

#### **3.2. CHALLENGES AND OPPORTUNITIES**

The cloud data center, public or private, is no longer a homogeneous footprint of commercial off-the-shelf (COTS) compute, storage, and networking. The continued demand for efficiency, the breadth of traditional enterprise and HPC applications being migrated to hybrid public/private clouds as well as the new cloud-native applications are admitting bespoke silicon solutions in compute, storage and networking, analogous to the advantage of heterogeneous core types employed by embedded systems for many years. The huge scale of problems in social networking and AI, for example, means that algorithms run at memory speed and that multiple processors are required to compute. The *radius of useful locality*—the distance over which programmers can use data as effectively local—is an important metric. We expect the combination of increasingly integrated high-radix photonic switches and open memory-semantic fabrics to greatly enlarge useful locality radius and diversity of compute and memory endpoints over the next few years. Memory bandwidth is a constraint on both core performance and number of cores per socket. Three dimensional scaling of memory at every level—layers-in-die, dice-in-stack, stacks-in-package or stacks-on-ASIC will contribute greater local and fabric attached bandwidth. Thermal power dissipation continues to be an important limit, and may need to be addressed down to inter-die and intra-die cooling.

Cloud systems present significant challenges. Heterogeneous architectures can provide more efficient computation of key functions. Novel memory systems, including stacked memories, offer high performance and lower power consumption. Advances in internal interconnect may create tipping points in system architecture.

#### **3.3. DESIGN ENVELOPE CONSIDERATIONS**

This category encompasses the largest and most power-hungry of systems, where we are more concerned with scalability than physical size as a constraint. At this macro level, we are concerned with geo-political issues regarding the siting of essentially immovable systems near to the resources needed to operate them, whilst mitigating the latency issues associated with large, distributed systems. Historically, we have tended to be less concerned with power issues as a driver within this envelope, however we must now recognize that the collective scale of these systems represent a global challenge. We face fundamental physical limits on our ability to deliver power into and extract heat out of industrial park-sized data centers. Thermal effects limit performance and may affect rack-level utilization. Power and thermal limitations have implications at all levels of the design hierarchy: building, rack, board, and chip. More significantly, continuing growth in demand for Cloud resources means that we

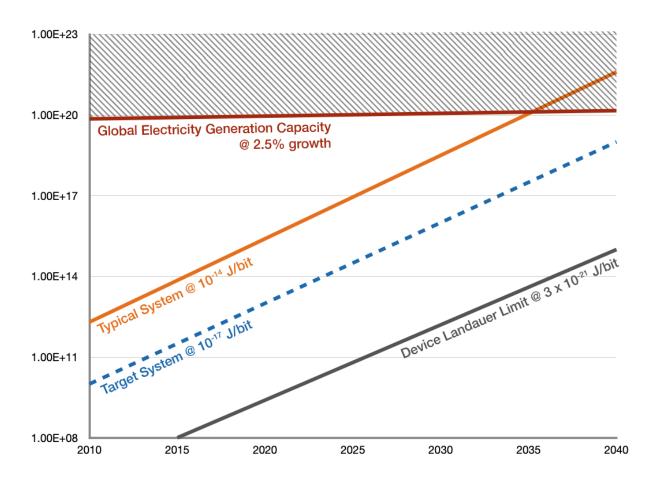

are still on a trajectory that shows data center workloads consuming all of the world's current electricity generating capacity, within the next 15 years. A reduction in transactional energy cost (J/bit) of at least three orders of magnitude is required in order to push that out by another decade.

Figure SA-2. Cloud Energy Usage based upon BIT Transition Cost

#### 3.3.1. TRENDS OF PROCESSORS FOR HIGH-END SYSTEMS

The power consumption of processors used for high-end systems such as cloud, servers, and high-performance computing ranges from tens of watt to a few hundreds of watt depending on the performance requirement of each processor chip and its cooling capacity. As these systems are composed of a cluster of multiple compute nodes, total system performance is usually a crucial metric rather than a single processor performance. Since the total system performance depends on the number of installed nodes which is mainly limited by total power and/or cooling budget of a data center facility, power efficiency, sometimes measured by performance per watt, is used to be a critical factor of the processors.

These types of processors have been and continue to be evolved in a different way to match with different workload characteristics: that needs lower latency, which needs throughput, and that needs compute capability. We assume three classes of high-end processors<sup>4</sup>.

1. Latency sensitive processors: these processors are optimized for lowering any aspect of latency, usually prioritizing single thread performance. They have a rich out-of-order execution resources with advanced branch prediction and cache prefetching mechanisms, a deeper cache hierarchy with relatively larger a last level cache, and large main memory with standard double data rate (DDR) technologies to accommodate a large dataset. Typical workload of cloud and server systems with these processors includes network services, database processing, and graph processing.

<sup>&</sup>lt;sup>4</sup> This classification is originally from NGACI white paper (https://sites.google.com/view/ngaci/home)

General purpose server class processors such as Intel Xeon, AMD EPYC, and Amazon Graviton are representative examples of these processors.

- 2. Throughput oriented processors: these processors are specially optimized for compute and data movement bandwidth, prioritizing parallel processing efficiency. They emphasize data level, thread level, and core level parallelism of the workload to achieve higher performance. In order to integrate more number of compute units, out-of-order execution resources and memory hierarchy are simplified. Integrated memory modules with high bandwidth memory (HBM) or graphics DDR (GDDR) are usually used to increase memory to processor bandwidth. Typical workloads of this type of processors are graphics and supercomputing applications. Representative examples of these processors are GPUs such as NVIDIA A100, A64FX used in Supercomputer Fugaku, and vector processors such as SX-Aurora Tsubasa.

- 3. Compute centric processors: these processors are specially designed for achieving very high compute throughput with less emphasis on main memory bandwidth. They usually have a large SRAM on-chip memory assuming dataset of the current workload fits in the on-chip memory. They can achieve very high compute density utilizing high bandwidth data supply from on-chip SRAM to functional units. Deep learning and inference applications are the main target of this type of processors. Representative examples of these processors include Cerebras WSE CS-2, Tesla D1, Esperanto ET, Graphcore Colossus MK2 GC200 IPU, Groq TSP, SambaNova SN10.

We forecast the technological trend of the latency sensitive processors and throughput oriented processors as shown in Table SA-2 and Table SA-3. In the forecast, we assume multiple dies are tightly connected in a package with chiplet technologies.

|                                                                 | 2019        | 2022         | 2024         | 2026         | 2028         | 2030         | 2032         | 2034         |

|-----------------------------------------------------------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| # chiplet per socket                                            | 4-8         | 8            | 8            | 8            | 8-16         | 8-16         | 8-16         | 16-20        |

| # core per chiplet                                              | 8           | 8            | 8-12         | 8-16         | 8-16         | 16-24        | 16-32        | 16-32        |

| # core per socket (max)                                         | 64          | 64           | 96           | 128          | 256          | 384          | 512          | 640          |

| Processor base frequency (GHz)<br>(for multiple cores together) | 2.2-3.0     | 2.5-3.3      | 2.8-3.4      | 3.0-3.5      | 3.2-3.6      | 3.4-3.7      | 3.4-3.7      | 3.4-3.7      |

| Core total vector length                                        | 1024        | 1024         | 1024         | 1024         | 2048         | 2048         | 2048         | 2048         |

| L1 data cache size (in KB)                                      | 36          | 40           | 40           | 42           | 42           | 44           | 44           | 44           |

| L1 instruction cache size (in KB)                               | 48          | 96           | 96           | 128          | 128          | 160          | 160          | 160          |

| L2 cache size (in MB)                                           | 1           | 1.5          | 2            | 2            | 2            | 2.5          | 2.5          | 2.5          |

| LLC cache size (in MB)                                          | 64-128      | 64-800       | 128-<br>1024 | 256-<br>1536 | 256-<br>2048 | 512-<br>4096 | 512-<br>4096 | 512-<br>4096 |

| # of DDR channels                                               | 8<br>(DDR4) | 12<br>(DDR4) | 12<br>(DDR5) | 12<br>(DDR5) | 16<br>(DDR5) | 16<br>(DDR6) | 16<br>(DDR6) | 16<br>(DDR6) |

| DDR bandwidth (TB/s)                                            | 0.20        | 0.31         | 0.61         | 0.76         | 1.02         | 1.1          | 1.2          | 1.2          |

| DDR size per socket (in TB)                                     | 1.0         | 3.0          | 4.5          | 6.0          | 8.0          | 10.0         | 12.0         | 12.0         |

| Socket max TDP (Watts)                                          | 280         | 300          | 400          | 450          | 600          | 600          | 700          | 700          |

Table SA-2. Technology Trends of Latency Sensitive Processors

L1=level 1 cache; LLC=last-level cache; Fabric=PCIe or new fabric (e.g. CXL); TDP=total power dissipation.

|                                                                    | 2019        | 2022        | 2024        | 2026        | 2028        | 2030         | 2032         | 2034         |

|--------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|

| # chiplet per socket                                               | 1           | 1           | 4           | 8-16        | 8-16        | 8-16         | 8-16         | 8-20         |

| # SM core per chiplet                                              | 108         | 132         | 36          | 36          | 42          | 48           | 54           | 54           |

| # core per socket (max)                                            | 108         | 132         | 144         | 288-576     | 336-672     | 384-768      | 432-864      | 432-1080     |