INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

# INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

# 2020 Edition

# **BEYOND CMOS**

THE IRDS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

© 2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# **Table of Contents**

| knowle                 | edgments                                                                                                                                                                                                                                                         | vi                                                                                                                                                                          |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Introc                 | luction                                                                                                                                                                                                                                                          | 1                                                                                                                                                                           |  |

| 1.1.                   | Scope of Beyond-CMOS Focus Team                                                                                                                                                                                                                                  | 1                                                                                                                                                                           |  |

| 1.2.                   | Difficult Challenges                                                                                                                                                                                                                                             | 2                                                                                                                                                                           |  |

| 1.3.                   | Nano-information Processing Taxonomy                                                                                                                                                                                                                             | 4                                                                                                                                                                           |  |

| Emer                   | ging Memory Devices                                                                                                                                                                                                                                              | 4                                                                                                                                                                           |  |

| 2.1.                   | Memory Taxonomy                                                                                                                                                                                                                                                  | 5                                                                                                                                                                           |  |

| 2.2.                   | Emerging Memory Devices                                                                                                                                                                                                                                          | 6                                                                                                                                                                           |  |

| 2.3.                   | Memory Selector Device                                                                                                                                                                                                                                           | 17                                                                                                                                                                          |  |

| 2.4.                   | Storage Class Memory                                                                                                                                                                                                                                             | 20                                                                                                                                                                          |  |

| Emer                   | ging Logic and Alternative Information Processing Devices                                                                                                                                                                                                        | 27                                                                                                                                                                          |  |

| 3.1.                   | Taxonomy                                                                                                                                                                                                                                                         | 27                                                                                                                                                                          |  |

| 3.2.                   | Devices for CMOS Extension                                                                                                                                                                                                                                       |                                                                                                                                                                             |  |

| 3.3.                   | Beyond-CMOS Devices: Charge-Based                                                                                                                                                                                                                                | 32                                                                                                                                                                          |  |

| 3.4.                   | Beyond-CMOS Devices: Alternative Information Processing                                                                                                                                                                                                          | 36                                                                                                                                                                          |  |

| Emer                   | ging Device-Architecture Interaction                                                                                                                                                                                                                             | 41                                                                                                                                                                          |  |

| 4.1.                   | Introduction                                                                                                                                                                                                                                                     | 41                                                                                                                                                                          |  |

| 4.2.                   | Analog Computing                                                                                                                                                                                                                                                 | 43                                                                                                                                                                          |  |

| 4.3.                   | Probabilistic Circuits                                                                                                                                                                                                                                           | 57                                                                                                                                                                          |  |

| 4.4.                   | Reversible Computing                                                                                                                                                                                                                                             |                                                                                                                                                                             |  |

| 4.5.                   | Device-Architecture Interaction: Conclusions/Recommendations                                                                                                                                                                                                     | 64                                                                                                                                                                          |  |

| Beyo                   | nd CMOS Devices for More-Than-Moore Applications                                                                                                                                                                                                                 | 64                                                                                                                                                                          |  |

| 5.1.                   | Emerging Devices for Security Applications                                                                                                                                                                                                                       | 64                                                                                                                                                                          |  |

| Emer                   | ging Materials Integration                                                                                                                                                                                                                                       | 68                                                                                                                                                                          |  |

| 6.1.                   | Introduction and Scope                                                                                                                                                                                                                                           | 68                                                                                                                                                                          |  |

| 6.2.                   | Challenges                                                                                                                                                                                                                                                       |                                                                                                                                                                             |  |

| 6.3.                   | Technology Requirements and Potential Solutions                                                                                                                                                                                                                  | 70                                                                                                                                                                          |  |

| 6.4.                   | Emerging/Disruptive Concepts and Technologies                                                                                                                                                                                                                    | 73                                                                                                                                                                          |  |

| 6.5.                   | Conclusions and Recommendations                                                                                                                                                                                                                                  | 74                                                                                                                                                                          |  |

| Asses                  | ssment                                                                                                                                                                                                                                                           | 74                                                                                                                                                                          |  |

| 7.1.                   | Introduction                                                                                                                                                                                                                                                     |                                                                                                                                                                             |  |

| 7.2.                   | NRI Beyond-CMOS Benchmarking                                                                                                                                                                                                                                     | 75                                                                                                                                                                          |  |

| 7.3.                   | Archive of ITRS ERD Survey-Based Assessment                                                                                                                                                                                                                      | 77                                                                                                                                                                          |  |

| . Summary              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                             |  |

| 9. Endnotes/References |                                                                                                                                                                                                                                                                  |                                                                                                                                                                             |  |

|                        | Introd<br>1.1.<br>1.2.<br>1.3.<br>Emer<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>Emer<br>3.1.<br>3.2.<br>3.4.<br>Emer<br>4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>Beyon<br>5.1.<br>Emer<br>6.1.<br>6.2.<br>6.3.<br>6.4.<br>6.5.<br>Asses<br>7.1.<br>7.2.<br>7.3.<br>Sumr | 1.1.       Scope of Beyond-CMOS Focus Team         1.2.       Difficult Challenges         1.3.       Nano-information Processing Taxonomy.         Emerging Memory Devices |  |

# List of Figures

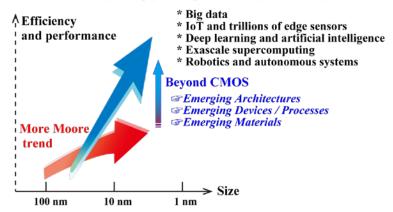

| Figure BC1.1  | Relationship of More Moore, Beyond CMOS, and Novel Computing Paradigms<br>and Applications (Courtesy of Japan beyond-CMOS group)                                                                                                                                | 1  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

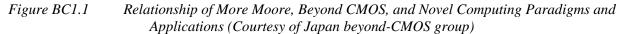

| Figure BC2.1  | Taxonomy of Emerging Memory Devices                                                                                                                                                                                                                             | 6  |

| Figure BC2.2. | Taxonomy of Memory Select Devices                                                                                                                                                                                                                               | 17 |

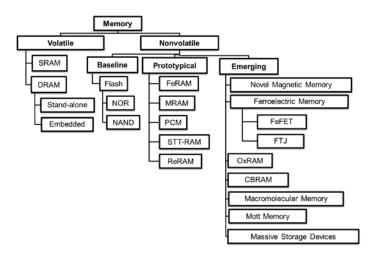

| Figure BC2.3  | Comparison of Performance of Different Memory Technologies                                                                                                                                                                                                      | 23 |

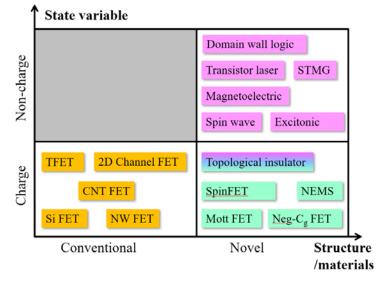

| Figure BC3.1  | Taxonomy of Options for Emerging Logic Devices                                                                                                                                                                                                                  | 27 |

| Figure BC4.1. | Conventional vs. Alternative Computing Paradigms                                                                                                                                                                                                                | 42 |

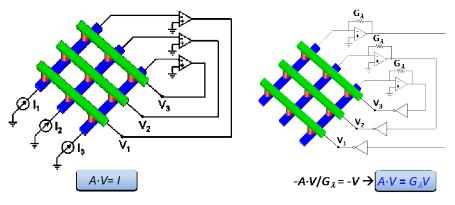

| Figure BC4.2  | A Resistive Memory Crossbar $Ax = b$ Solver is Illustrated                                                                                                                                                                                                      | 45 |

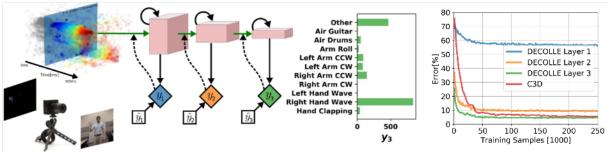

| Figure BC4.3  | A Spiking CNN for Gesture Recognition with Local Learning                                                                                                                                                                                                       | 47 |

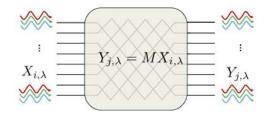

| Figure BC4.4  | One Generalized Instantiation of a Photonic MVM unit, with Wavelength Multiplexed Inputs and Outputs and a Coupler-based Tunable Array. Reproduced from <sup>931</sup>                                                                                          | 54 |

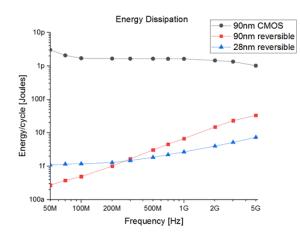

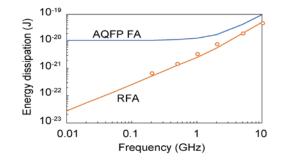

| Figure BC4.5  | Energy Dissipation per Stage vs. Frequency in an Adiabatic CMOS Shift<br>Register                                                                                                                                                                               |    |

| Figure BC4.6  | Energy dissipation of RQFP and irreversible AQFP 1-b full adders                                                                                                                                                                                                | 62 |

| Figure EMI1   | Emerging Material Integration Promotes the Advancement of Existing<br>Technologies                                                                                                                                                                              | 69 |

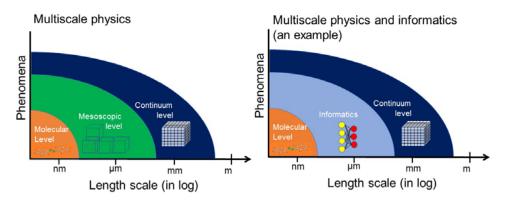

| Figure EMI2   | An Example of the Role of Machine Learning in the Multiscale Simulation                                                                                                                                                                                         | 74 |

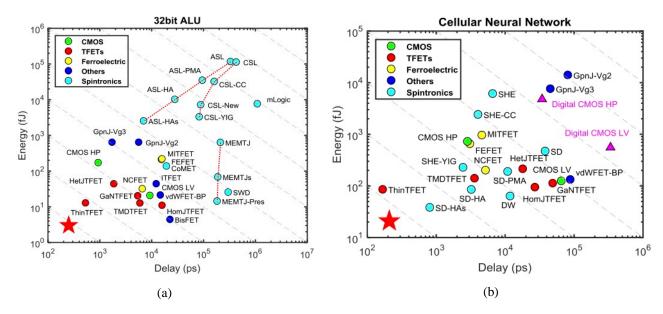

| Figure BC7.1  | (a) Energy versus Delay of a 32-bit ALU for a Variety of Charge- and Spin-<br>based Devices; (b) Energy versus Delay per Memory Association Operation<br>Using Cellular Neural Network (CNN) for a Variety of Charge- and Spin-based<br>Devices <sup>1156</sup> | 76 |

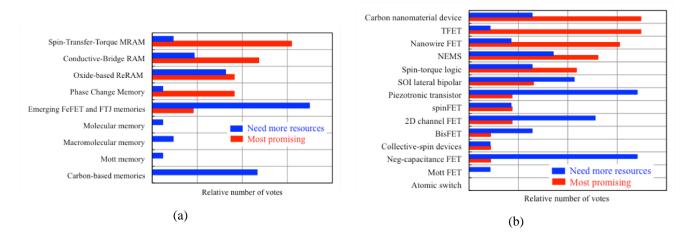

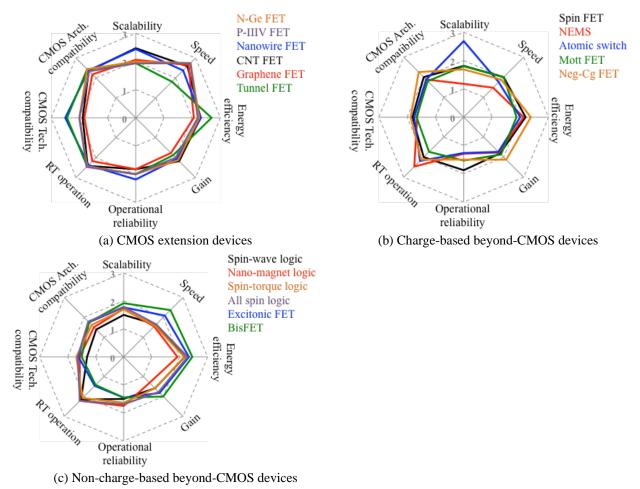

| Figure BC7.2  | (a) Survey of Emerging Memory Devices and (b) Survey of Emerging Logic Devices in 2014 ERD Emerging Logic Workshop (Albuquerque, NM)                                                                                                                            | 78 |

| Figure BC7.3  | Comparison of Emerging Memory Devices Based on 2013 Critical Review                                                                                                                                                                                             | 78 |

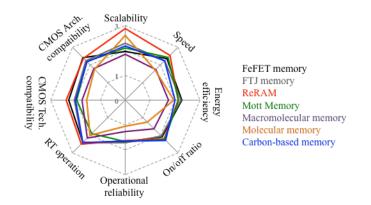

| Figure BC7.4  | Comparison of Emerging Logic Devices Based on 2013 ITRS ERD Critical<br>Review: (a) CMOS Extension Devices; (b) Charge-based Beyond-CMOS<br>Devices; (c) Non-charge-based Beyond-CMOS Devices                                                                   | 79 |

# List of Tables

| Table BC1.1  | Beyond CMOS Difficult Challenges                                                                       | 3  |

|--------------|--------------------------------------------------------------------------------------------------------|----|

| Table BC2.1  | Emerging Research Memory Devices—Demonstrated and Projected Parameters                                 | 5  |

| Table BC2.2  | Experimental Demonstrations of Vertical Transistors in Memory Arrays                                   | 18 |

| Table BC2.3  | Benchmark Select Device Parameters                                                                     | 18 |

| Table BC2.4a | Experimentally Demonstrated Two-terminal Memory Select Devices                                         | 20 |

| Table BC2.4b | Experimentally Demonstrated Self-selecting Memory Devices (self-rectifying)                            |    |

| Table BC2.5  | Target Device and System Specifications for SCM                                                        | 22 |

| Table BC2.6  | Potential of Current Prototypical and Emerging Research Memory Candidates for SCM Applications         | 22 |

| Table BC2.7. | Likely Desirable Properties of M (Memory) Type and S (Storage) Type Storage Class Memories             |    |

| Table BC3.1a | MOSFETS: Extending MOSFETs to End of Roadmap                                                           | 27 |

| Table BC3.1b | Charge-based Beyond CMOS: Non-conventional FETs and Other Charge-<br>based Information Carrier Devices | 27 |

| Table BC3.1c | Alternative Information Processing Devices                                                             | 28 |

| Table BC4.1  | Metrics for Analog Capacitive Vector-Matrix Multiply (VMM) ICs                                         | 54 |

| Table BC4.2  | Comparison of Some Electrical Oscillators for Computing                                                | 56 |

| Table EMI1   | Near-term Difficult Challenges                                                                         | 69 |

| Table EMI2   | Long-term Difficult Challenges                                                                         | 70 |

| Table EMI3   | Materials for Transistor Scaling and Integration                                                       | 71 |

| Table EMI4   | Materials for Lithography and Patterning                                                               | 71 |

| Table EMI5   | Interconnect Materials                                                                                 | 71 |

| Table EMI6   | Heterogeneous Integration, Assembly and Packaging Materials                                            | 72 |

| Table EMI7   | Emerging Research Materials Needs for Outside System Connectivity                                      | 72 |

| Table EMI8   | Emerging Materials for Memory                                                                          | 72 |

| Table EMI9   | Emerging Materials for Memory Select                                                                   | 72 |

| Table EMI10  | Emerging Materials for Advanced and Beyond-CMOS Logic Devices                                          |    |

| Table EMI11  | Spin Devices versus Materials                                                                          | 73 |

| Table EMI12  | Spin Material Requirements and Properties                                                              | 73 |

| Table EMI13  | Metrology Needs and Challenges for Emerging Research Materials                                         | 73 |

| Table EMI14  | Modeling and Simulation                                                                                | 74 |

| Table EMI15  | Summary of Potentially Disruptive Emerging Research Materials Application<br>Opportunities             | 74 |

# ACKNOWLEDGMENTS

Sapan Agarwal Brad Aimone Hiro Akinaga Otitoaleke Akinola Mustafa Badaroglu Gennadi Bersuker Christian Binek Geoffrey Burr Leonid Butov Kerem Camsari Gert Cauwenberghs An Chen Winston Chern Supriyo Datta John Dallesasse Shamik Das Erik DeBenedictis Peter Dowben Tetsuo Endoh **Ben Feinberg** Thomas Ferreira de Lima Akira Fujiwara Elliot Fuller Michael Frank Paul Franzon Michael Fuhrer Mike Garner Chakku Goplan Bogdan Govoreanu Cat Graves Kohei Hamaya Masami Hane Jennifer Hasler Yoshihiro Hayashi **Toshiro Hiramoto** D. Scott Holmes Sharon Hu Francesca Iacopi Danielle Ilmeni Jean Anne Incorvia Engin Ipek Satoshi Kamiyama Kiyoshi Kawabata Asif Khan Hajime Kobayashi Suhas Kumar Ilya Krivorotov Xiuling Li Xiang (Shaun) Li

Shy-Jay Lin Tsu-Jae King Liu Matthew Marinella Bicky A. Marque Rivu Midya Yoshiyuki Miyamoto Johannes Muller Azad Naeemi Mitchell A. Nahmias Emre Neftci Mike Niemier Dmitri Nikonov Yutaka Ohno Chenyun Pan Ferdinand Peper Shriram Ramanathan Mingyi Rao Shashi Paul Paul R. Prucnal **Titash Rakshit** Arijit Raychowdhury Sayeef Salahuddin Shintaro Sato Michael Schneider Bhavin J. Shastri Xia Sheng Takahiro Shinada Urmita Sikder Greg Snider John-Paul Strachan Dimitri Strukov Naoyuki Sugiyama Tarek Taha Alexander N. Tait Shinichi Takagi Norikatsu Takaura Tsutomu Teduka Yasuhide Tomioka Wilman Tsai Tohru Tsuruoka Zhongrui Wang R. Stanley Williams Justin Wong Dirk Wouters Patrick Xiao Kojiro Yagami J. Joshua Yang Noboyuki Yoshikawa Victor Zhirnov

# BEYOND CMOS

# **1. INTRODUCTION**

# 1.1. SCOPE OF BEYOND-CMOS FOCUS TEAM

Dimensional and functional scaling<sup>1</sup> of CMOS is driving information processing<sup>2</sup> technology into a broadening spectrum of new applications. Scaling has enabled many of these applications through increased performance and complexity. As dimensional scaling of CMOS will eventually approach fundamental limits, several new information processing devices and microarchitectures for both existing and new functions are being explored to extend the historical integrated circuit scaling cadence. This is driving interest in new devices for information processing and memory, new technologies for heterogeneous integration of multiple functions, and new paradigms for system architecture. This chapter, therefore, provides an IRDS perspective on emerging research device technologies and serves as a bridge between conventional CMOS and the realm of nanoelectronics beyond the end of CMOS scaling.

An overarching goal of this chapter is to survey, assess, and catalog viable emerging devices and novel architectures for their long-range potential and technological maturity and to identify the scientific/technological challenges gating their acceptance by the semiconductor industry as having acceptable risk for further development. This chapter also surveys beyond-CMOS devices for more than Moore (MtM) applications, e.g., hardware security.

This goal is accomplished by addressing two technology-defining domains: 1) extending the functionality of the CMOS platform via heterogeneous integration of new technologies ("More Moore"), and 2) stimulating invention of new information processing paradigms ("Beyond CMOS"). The relationship between these domains is schematically illustrated in Figure BC1.1. Novel computing paradigms and application pulls (e.g., big data, IoT, artificial intelligence, autonomous systems, exascale computing) introduce higher performance and efficiency requirements, which is increasingly difficult for the saturating More Moore technologies to fulfill. Beyond-CMOS technologies may provide the required devices, processes, and architectures for the new era of computing.

## Novel computing paradigms and application pulls

The chapter is intended to provide an objective, informative resource for the constituent nanoelectronics communities pursuing: 1) research, 2) tool development, 3) funding support, and 4) investment. These communities include universities, research institutes, and industrial research laboratories; tool suppliers; research funding agencies; and the semiconductor industry. The potential and maturity of each emerging research device and architecture technology are reviewed and assessed to identify the

<sup>&</sup>lt;sup>1</sup> Functional Scaling: Suppose that a system has been realized to execute a specific function in a given, currently available, technology. We say that system has been functionally scaled if the system is realized in an alternate technology such that it performs the identical function as the original system and offers improvements in at least one of size, power, speed, or cost, and does not degrade in any of the other metrics.

<sup>&</sup>lt;sup>2</sup> Information processing refers to the input, transmission, storage, manipulation or processing, and output of data. The scope of the BC Chapter is restricted to data or information manipulation, transmission, and storage.

most important scientific and technological challenges that must be overcome for a candidate device or architecture to become a viable approach.

The chapter is divided into five sections: 1) emerging memory devices, 2) emerging logic and alternative information processing devices, 3) emerging device-architecture interaction, 4) beyond-CMOS devices for More-than-Moore applications, and 5) emerging materials integration. The former IRDS Emerging Research Materials (ERM) chapter is rolled into this chapter as section 6 renamed to "emerging materials integration". Some detail is provided for each entry regarding operation principles, advantages, technical challenges, maturity, and current and projected performance. The chapter also discusses applications and architectural focus combining emerging research devices offering specialized, unique functions as heterogeneous core processors integrated with a CMOS platform technology. This represents the nearer term focus of the chapter, with the longer-term focus remaining on discovery of an alternate information processing technology beyond digital CMOS.

# **1.2. DIFFICULT CHALLENGES**

### 1.2.1. INTRODUCTION

The semiconductor industry is facing some difficult challenges related to extending integrated circuit technology to new applications and to beyond the end of CMOS dimensional scaling. One class relates to propelling CMOS beyond its ultimate density and functionality by integrating a new high-speed, high-density, and low-power memory technology onto the CMOS platform. Another class is to extend CMOS scaling with alternative channel materials. The third class is information processing technologies substantially beyond those attainable by CMOS using an innovative combination of new devices, interconnect, and architectural approaches for extending CMOS and eventually inventing a new information processing platform technology. The fourth class is to extend ultimately scaled CMOS as a platform technology into new domains of functionalities and application, also known as "more than Moore". The fifth class is to bridge the gap between novel devices and unconventional architectures and computing paradigms. These difficult challenges are summarized in Table BC1.1.

### 1.2.2. DEVICE TECHNOLOGIES

Difficult challenges gating development of beyond-CMOS devices include those related to memory technologies, information processing or logic devices, and heterogeneous integration of multi-functional components, a.k.a. More-than-Moore (MtM) or Functional Diversification.

One challenge is the need of a new memory technology that combines the best features of current memories in a fabrication technology compatible with CMOS process flow and that can be scaled beyond the present limits of SRAM and FLASH. This would provide a memory device fabrication technology required for both stand-alone and embedded memory applications. The ability of an MPU to execute programs is limited by interaction between the processor and the memory, and scaling does not automatically solve this problem. The current evolutionary solution is to increase MPU cache memory, thereby increasing the floor space that SRAM occupies on an MPU chip. This trend eventually leads to a decrease of the net information throughput. In addition to auxiliary circuitry to maintain stored data, volatility of semiconductor memory requires external storage media with slow access (e.g., magnetic hard drives, optical CD, etc.). Therefore, development of electrically accessible non-volatile memory with high speed and high density would initiate a revolution in computer architecture. This development would provide a significant increase in information throughput beyond the traditional benefits of scaling when fully realized for nanoscale CMOS devices.

A related challenge is to sustain scaling of CMOS logic technology. One approach to continuing performance gains as CMOS scaling matures in the next decade is to replace the strained silicon MOSFET channel (and the source/drain) with an alternate material offering a higher potential quasi-ballistic-carrier velocity and higher mobility than strained silicon. Candidate materials include strained Ge, SiGe, a variety of III-V compound semiconductors, and carbon materials. Introduction of non-silicon materials into the channel and source/drain regions of an otherwise silicon MOSFET (i.e., onto a silicon substrate) is fraught with several very difficult challenges. These challenges include heterogeneous fabrication of high-quality (i.e., defect free) channel and source/drain materials on non-lattice matched silicon, minimization of band-to-band tunneling in narrow bandgap channel materials, elimination of Fermi level pinning in the channel/gate dielectric interface, and fabrication of high- $\kappa$  gate dielectrics on the passivated channel materials. Additional challenges are to sustain the required reduction in leakage currents and power dissipation in these ultimately scaled CMOS gates and to introduce these new materials into the MOSFET while simultaneously minimizing the increasing variations in critical dimensions and statistical fluctuations in the channel (source/drain) doping concentrations.

The industry is now addressing the increasing importance of a new trend of functional diversification, where added value to devices is provided by incorporating functionalities that do not necessarily scale according to "Moore's Law". In this chapter, an "Beyond-CMOS devices for More-than-Moore Applications" section covers unconventional applications of existing and novel technologies. The section currently covers emerging devices for hardware security and will be expanded in future update.

| Difficult Challenges                                                                                                                        | Summary of Issues and Opportunities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scale high-speed, dense, embeddable, volatile/non-volatile<br>memory technologies to replace SRAM and FLASH in<br>appropriate applications. | The scaling limits of SRAM and FLASH in 2D are driving the need for new memory technologies to replace SRAM and FLASH memories.<br>Identify the most promising technical approach(es) to obtain electrically accessible, high-speed, high-density, low-power, (preferably) embeddable volatile and non-volatile memories.<br>The desired material/device properties must be maintained through and after high temperature and corrosive chemical processing. Reliability issues should be identified and addressed early in the technology development.                                                                                                                                                                                                                                                                   |

| Extend CMOS scaling                                                                                                                         | Develop new materials to replace silicon (or III-V, Ge) as alternate channel and source/drain to increase the saturation velocity and to further reduce $V_{dd}$ and power dissipation in MOSFETs while minimizing leakage currents<br>Develop means to control the variability of critical dimensions and statistical distributions (e.g., gate length, channel thickness, S/D doping concentrations, etc.)<br>Accommodate the heterogeneous integration of dissimilar materials.<br>The desired material/device properties must be maintained through and after high temperature and corrosive chemical processing. Reliability issues should be identified and addressed early in this development.                                                                                                                    |

| Continue functional scaling of information processing<br>technology substantially beyond that attainable by ultimately<br>scaled CMOS.      | Invent and reduce to practice a new information processing technology to replace CMOS as<br>the performance driver.<br>Ensure that a new information processing technology has compatible memory technologies<br>and interconnect solutions.<br>A new information processing technology must be compatible with a system architecture that<br>can fully utilize the new device. Non-binary data representations or non-Boolean logic may<br>be required to employ a new device for information processing, which will drive the need for<br>new system architectures.<br>Bridge the gap that exists between materials behaviors and device functions.<br>Accommodate the heterogeneous integration of dissimilar materials.<br>Reliability issues should be identified and addressed early in the technology development. |

| Extend ultimately scaled CMOS as a platform technology<br>into new domains of functionalities and application ("more<br>than Moore, MtM").  | Discover and reduce to practice new device technologies and primitive-level architecture to provide special purpose optimized functional cores (e.g., accelerator functions) heterogeneously integrable with CMOS.<br>Provide added value by incorporating functionalities that do not necessarily scale according to "Moore's Law".<br>Heterogeneous integration of digital <i>and</i> non-digital functionalities into compact systems that will be the key driver for a wide variety of application fields, such as communication, automotive, environmental control, healthcare, security, and entertainment.                                                                                                                                                                                                         |

| Bridge the gap between novel devices and unconventional architectures and computing paradigms.                                              | Identify suitable opportunities in unconventional architectures and computing paradigms that<br>can utilize unique characteristics of novel devices.<br>Identify emerging devices that can implement computing functions and architectures more<br>efficiently than CMOS and Boolean logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Table BC1.1 Beyond CMOS Difficult Challenges

A longer-term challenge is invention and reduction to practice of a manufacturable information processing technology addressing "beyond CMOS" applications. For example, emerging research devices might be used to realize special purpose processor cores that could be integrated with multiple CMOS CPU cores to obtain performance advantages. These new special purpose cores may provide a particular system function much more efficiently than a digital CMOS block, or they may offer a uniquely new function not available in a CMOS-based approach. Solutions to this challenge beyond the end of CMOS gate as a new information processing primitive element. A new information processing technology must also be compatible with a system architecture that can fully utilize the new device. A non-binary data representation and non-Boolean logic may be required to employ a new device for information processing. These requirements will drive the need for new system architectures. The requirements and opportunities correlating emerging devices and architectures are discussed in the "Emerging Device-Architecture Interaction" section.

### 1.2.3. MATERIALS TECHNOLOGIES

The most difficult challenge for Beyond CMOS is to deliver materials with controlled properties that will enable operation of emerging research devices in high density at the nanometer scale. To improve control of material properties for high-density devices, research on materials synthesis must be integrated with work on new and improved metrology and modeling. These important objectives are addressed in the "Emerging Materials Integration" section.

#### **1.3. NANO-INFORMATION PROCESSING TAXONOMY**

Information processing systems to accomplish a specific function, in general, require several different interactive layers of technology. One comprehensive top-down list of these layers begins with the required application or system function, leading to system architecture, micro- or nano-architecture, circuits, devices, and materials. A different bottom-up representation of this hierarchy begins with the lowest physical layer represented by a computational state variable and ends with the highest layer represented by the architecture. In this representation focused on generic information processing at the device/circuit level, a fundamental unit of information (e.g., a bit) is represented by a computational state variable, for example, the position of a bead in the ancient abacus calculator or the charge (or voltage) state of a node capacitance in CMOS logic. The electronic charge as a binary computational state variable serves as the foundation for the von Neumann computational system architecture. A device provides the physical means of representing and manipulating a computational state variable among its two or more allowed discrete states. Eventually, device concepts may transition from simple binary switches to devices with more complex information processing functionality, perhaps with multiple fan-in and fan-out. The device is a physical structure resulting from the assemblage of a variety of materials possessing certain desired properties obtained through exercising a set of fabrication processes. An important layer, therefore, encompasses the various materials and processes necessary to fabricate the required device structure, which is a focus of the "Beyond CMOS (BC)" chapter. The data representation is how the computational state variable is encoded by the assemblage of devices to process the bits or data. Two of the most common examples of data representation are binary digital and continuous or analog signal. This layer is within the scope of the BC chapter. The architecture layer encompasses three subclasses of this taxonomy: 1) nano-architecture or the physical arrangement or assemblage of devices to form higher level functional primitives to represent and execute a computational model, 2) the computational model that describes the algorithm by which information is processed using the primitives, e.g., logic, arithmetic, memory, cellular nonlinear network (CNN), and 3) the system-level architecture that describes the conceptual structure and functional behavior of the system exercising the computational model.

# 2. EMERGING MEMORY DEVICES

The emerging research memory technologies tabulated in this section are a representative sample of published research efforts (circa 2017 - 2019) describing alternative approaches to established memory technologies.<sup>3</sup> The scope of this section also includes updated subsections addressing the "Select Device" required for a crossbar memory application and an updated treatment of "Storage Class Memory" (including Solid State Disks).

Figure BC2.1 is a taxonomy of the prototypical and emerging memory technologies. An overarching theme is the need to monolithically integrate each of these memory options onto a CMOS technology platform in a seamless manner. Fabrication technologies are sought that are modifications of or additions to established CMOS platform technologies. A goal is to provide the end user with a device that behaves similarly to the familiar silicon memory chip.

This memory portion of this section is organized around a set of eight technology entries shown in the column headers of Table BC2.1. These entries were selected using a systematic survey of the literature to determine areas of greatest worldwide research activity. Each technology entry listed has several sub-categories of devices that are grouped together to simplify the discussion. Key parameters associated with the technologies are listed in the table. For each parameter, two values for performance are given: 1) theoretically predicted performance values based on calculations and early experimental demonstrations, 2) up-to-date experimental values of these performance parameters reported in the cited technical references.

The tables have been extensively footnoted, and details may be found in the indicated references. The text associated with the table gives a brief summary of the operating principles of each device and significant scientific and technological issues, not captured in the table, but which must be resolved to demonstrate feasibility.

The purpose of many memory systems is to store massive amounts of data, and therefore memory capacity (or memory density) is one of the most important system parameters. In a typical memory system, the memory cells are connected to form a two-

<sup>&</sup>lt;sup>3</sup> Including a particular approach in this section does not in any way constitute advocacy or endorsement. Conversely, not including a particular concept in this section does not in any way constitute rejection of that approach. This listing does point out that existing research efforts are exploring a variety of basic memory mechanisms.

dimensional array, and it is essential to consider the performance of memory cells in the context of this array architecture. A memory cell in such an array can be viewed as being composed of two fundamental components: the 'storage node' and the 'select device', the latter of which allows a given memory cell in an array to be addressed for read or write. Both components impact scaling limits for memory. For several emerging resistance-based memories, the storage node can, in principle, be scaled down below 10 nm,<sup>1</sup> and the memory density will be limited by the select device. Planar transistors (e.g. FET or BJT) are typically used as select devices. In a two-dimensional layout using in-plane select FETs the cell layout area is Acell= $(6-8)F^2$ . In order to reach the highest possible 2-D memory density of  $4F^2$ , a vertical select transistor can be used. Table BC2.3 shows several examples of vertical transistor approaches. Another approach to obtaining a select device with a small footprint is a two-terminal nonlinear device, e.g. a diode. Table BC2.4 displays benchmark parameters required for a 2-terminal select device, and Table BC2.5 summarizes the operating parameters for several candidate 2-terminal select devices.

Storage-class memory (SCM) describes a device category that combines the benefits of solid-state memory, such as high performance and robustness, with the archival capabilities and low cost per bit of conventional hard-disk magnetic storage. Such a device requires a non-volatile memory technology that can be manufactured at a very low cost per bit. Table BC2.6 lists a representative set of target specifications for SCM devices and systems, which are compared against benchmark parameters offered by existing technologies (HDD, NAND Flash, and DRAM). Two columns are shown, one for the slower S-class Storage Class Memory, and one for fast M-class SCM, as described in Section 2.4. These numbers describe the performance characteristics that will likely be required from one or more emerging memory devices in order to enable the emerging application space of Storage Class Memory. Table BC2.7 illustrates the potential for storage-class memory applications of a number of prototypical memory technologies (Table BC2.1) and emerging research memory candidates (Table BC2.2). The table shows qualitative assessments across a variety of device characteristics, based on the target system parameters from Table BC2.6. These tables are discussed in more detail in Section 2.4.

Table BC2.1

Emerging Research Memory Devices—Demonstrated and Projected Parameters

# 2.1. MEMORY TAXONOMY

Figure BC2.1 provides a simple visual method of categorizing memory technologies. At the highest level, memory technologies are separated by the ability to retain data without power. Non-volatile memory offers essential use advantages, and the degree to which non-volatility exists is measured in terms of the length of time that data can be expected to be retained. Volatile memories also have a characteristic retention time that can vary from milliseconds to (for practical purposes) the length of time that power remains on. Non-volatile memory technologies are further categorized by their maturity. Flash memory is considered the baseline non-volatile memory because it is highly mature, well optimized, and has a significant commercial presence. Flash memory is the benchmark against which prototypical and emerging non-volatile memory technologies are measured. Prototypical memory technologies are at a point of maturity where they are commercially available (generally for niche applications), and have a large scientific, technological, and systems knowledge base available in the literature. The focus of this section is Emerging Memory Technologies. These are the least mature memory technologies in Figure BC2.1, but they have been shown to offer significant potential benefits if various scientific and technological hurdles can be overcome. This section provides an overview of these emerging technologies, their potential benefits, and the key research challenges that will allow them to become viable commercial technologies.

Figure BC2.1 Taxonomy of Emerging Memory Devices

# 2.2. EMERGING MEMORY DEVICES

#### 2.2.1. NOVEL MAGNETIC MEMORIES

This section is divided into three categories of devices based on different mechanisms, i.e., spin-transfer torque, spin-orbital torque, and voltage-controlled magnetic anisotropy.

#### 2.2.1.1. SPIN-TRANSFER TORQUE

Spin-transfer torque (STT) MRAM has recently entered the commercial production stage for both embedded and standalone Flash-like applications. Various foundries announce the readiness of embedded MRAM (TSMC, GlobalFoundries, Samsung) for production, and standalone MRAM products with various density (Mb-Gb) are also available on the market for IoT and data center applications (Avalanche Tech, Everspin). For embedded applications, STT-MRAM possesses non-volatility, high-endurance, scalability, low power, and fewer masks than the embedded Flash.<sup>2</sup> It also provides great area savings and lower leakage compared with SRAM. A STT-MRAM cell consists of a magnetic tunnel junction (MTJ) with two ferromagnetic layers, i.e. a free layer (FL) and a reference layer (RL) sandwiching a tunnel barrier. When a current enters the RL, the electrons' spin is polarized according to that of the RL. After tunneling through to the FL, the spin momentum of these spin-polarized electrons is transferred to the FL, thus writing the FL orientation to that of the RL. The opposite operation can be achieved by flipping the current polarity. Compared with its in-plane counterpart, perpendicular STT-MRAM has higher density, lower switching current, and is easier to control in large scale manufacturing.<sup>3</sup>

Since Flash-like STT-MRAM is entering mass production at all major foundries, this topic is covered in the More Moore Chapter of IRDS. For cache-level applications, research has shown 3 ns, 63  $\mu$ A switching of 16-nm perpendicular STT-MRAM with endurance above 10<sup>12</sup> cycles and WER below 10<sup>-6</sup>.<sup>4</sup> Reliable 10 ns, 0.12 pJ switching of 50  $\mu$ A with sub-ppm error rates is also recently demonstrated in 30 nm perpendicular STT-MTJs satisfying the last level cache (LLC) application requirements.<sup>5</sup> A system-level benchmarking study also indicates the use of 34 nm perpendicular STT-MRAM to replace SRAM as a LLC for high performance computing (HPC) at 5 nm node provides significant read and write energy gains at about 43% of the total macro area, achieving a nominal access latency <2.5 ns and <7.1 ns for read and write respectively.<sup>6</sup> (see Table BC2.1)

For SRAM-like STT-MRAM development, a major challenge is to reduce the write power consumption at sub-10 ns write speed. The large write power at sub-ns speed using STT requires a large access transistor, reducing density as well as reduced endurance due to tunnel barrier damage from higher writing current. Multiple factors contribute to this high switching current at sub-10 ns regime including limited spin torque efficiency, incubation delay, and intrinsic magnetization precession frequency on the order of GHz. A great amount of work has been devoted to increasing the switching speed, such as decreasing the FL saturation magnetization, lowering the FL damping factor,<sup>7</sup> and increasing the STT effect via double-RL design<sup>8</sup>. However, because at most 100% of the current can be polarized, there is an upper bound of the write efficiency using the STT effect. In contrast, the use of writing mechanisms of fundamentally different physics, such as spin-orbit torque (SOT) and voltage-controlled magnetic anisotropy (VCMA) effect, may help propel the next-generation of MRAM technologies for SRAM-like cache applications. Secondly, as the critical dimension of STT-MRAM scales down to less than 20 nm, the requirement of thermal stability calls for higher interfacial perpendicular magnetic anisotropy (PMA). Double-MgO barrier MTJs have shown 2x improvement in MTJ

with diameters above 10 nm,<sup>9</sup> whereas the use of shape-anisotropy induced PMA from elongated ferromagnetic pillars may further the scaling of STT-MRAM below 10 nm diameter.<sup>10</sup> Lastly, STT-MRAM with higher density to replace DRAM is still an open area for research. Stacking of STT-MRAM dies with logic or memory dies using through silicon vias,<sup>11,12</sup> and high density 3D integration of STT-MRAM using selector-MTJ crossbar architecture<sup>13</sup> are two high potential approaches.

#### 2.2.1.2. SPIN-ORBIT TORQUE

Spin-orbit torque (SOT)-driven magnetization switching recently emerges as an alternative write mechanism beyond STT for SRAM-like cache-level applications. Though at rather early stage of research, sub-ns SOT writing has been demonstrated at current density of 20-40 MA/cm<sup>2</sup>.<sup>14,15</sup> compared with 3-10 ns switching of STT-MRAM at a current density of 7 MA/cm<sup>2</sup>.<sup>5,16</sup>(see Table BC2.1). A SOT-MRAM cell consists of a magnetic tunnel junction (MTJ) with its free layer (FL) sitting on top of a strip of material with large spin-orbit coupling (SOC), such as heavy metal<sup>17,18</sup>. When current flows through this long strip of SOT material, spin-polarized current emerges and diffuses into the adjacent FL. Like the STT case, the spin-polarized current exerts a damping-like spin torque on the ferromagnetic layer, thus switching the FL orientation. As the write path is separated from the read path, a much larger read voltage can increase read speed. The major advantage of SOT over STT is that unlike STT where the filtered spin-polarized current is smaller than the charge current, the SOT efficiency (spin-polarized current over charge current) can be larger than one in the SOT case.<sup>19</sup> From a physics perspective, multiple mechanisms have been found to contribute to this large damping-like SOT, including spin Hall effect (SHE)<sup>17</sup>, Rashba-Edelstein effect<sup>18</sup>, and spin-momentum locking from topological protected electronic states<sup>19</sup>. Most experimental work has discovered a damping-like SOT in the in-plane transverse direction with respect to the current flow direction. However, there also exists a field-like SOT in many of the experimental works, which acts on the free layer like a static magnetic field with a fixed orientation.

There are three types of SOT-MRAM configurations, i.e., in-plane MTJ with easy axis oriented along the current direction (type X), in-plane MTJ with easy axis oriented orthogonal to the current direction (type Y), and perpendicular MTJ (type Z). Note that only type Y can achieve field-free switching, while both type X and Z require the breaking of symmetry for deterministic switching. Experimentally, 0.5-ns switching with a current density of 40 MA/cm<sup>2</sup> has been demonstrated in a 100 x 400 nm<sup>2</sup> type X MTJ, which will lead to 51- $\mu$ A, 0.3-V, and 8-fJ write performance when scaled down to a channel width of 50 nm.<sup>14</sup> Another work shows 0.5-ns switching with a current density of 18 MA/cm<sup>2</sup> in 30 x 190 cm<sup>2</sup> type Y MTJ with a write error rate (WER) of 10<sup>-6</sup>.<sup>15</sup> For perpendicular MTJ (type Z), research has shown 0.5-ns and 220-fJ write operation with a current density of 180 MA/cm<sup>2</sup> of a 60 nm perpendicular MTJ with endurance up to 10<sup>11</sup> and WER down to 10<sup>-5</sup>. Field-free switching is realized in this work by using an elongated biasing ferromagnet deposited on top of the SOT-MTJ.<sup>20</sup>

Lowering the write energy while maintaining sub-ns switching speed is the main challenge to push SOT-MRAM into cache-level applications. A multitude of novel SOT materials beyond traditional heavy metal are being intensively investigated for higher SOT efficiency. Several new research directions include heavy metal alloys<sup>21</sup>, topological insulator and semimetal<sup>22,23</sup>, antiferromagnets<sup>24,25</sup>, and complex oxides<sup>26,27</sup>. The need of high SOT efficiency is especially critical for type Z as it inherently shows a larger switching current than type X and Y<sup>28</sup>. Second, SOT-MRAM suffers from a large cell size due to the three-terminal configuration needed to perform separate write and read functions.<sup>29</sup> A two-terminal perpendicular SOT-MRAM has been demonstrated by increasing the density of the current flowing in-plane in the SOT underlayer while suppressing that of the current flowing perpendicular in the MTJ<sup>30</sup>. Meanwhile, the scheme of multiple SOT-MTJs sharing one single SOT write line can partially alleviate the density disadvantage of SOT-MRAM.<sup>31</sup> Third, a tradeoff exists between writing speed and field-free switching. For type Y, the FL aligning to the transverse direction does not experience any SOT; thus, an initial perturbation of the FL away from the easy axis is required for fast switching. A large field-like SOT or Oersted field due to SOT current can provide this perturbation.<sup>32</sup> For type X and Z, a maximal SOT exists as the FL is aligned perpendicular to the spin current direction, thus enabling high-speed switching. There have been several approaches to break the symmetry for realizing field-free type X and Z switching, such as lateral structural and shape-induced asymmetry<sup>28,33,34</sup>, use of interlayer exchange coupling<sup>35</sup>, exchange bias<sup>24</sup>, and dipolar external magnetic field<sup>36</sup>. Meanwhile, new studies show field-free switching of type Z MTJ using a dampinglike SOT with perpendicular polarization arising from crystalline materials with broken in-plane symmetry<sup>37</sup> and interfaces with SOC<sup>38,39</sup>. Last, the scalability of all three SOT types remains an open question. Type X and Y scaling are challenging due to variations in MTJ shape, while type X and Z scaling face obstacles in implementing field-free switching at scaled nodes.

#### 2.2.1.3. VOLTAGE-CONTROLLED MAGNETIC ANISOTROPY

Contrary to current-driven writing mechanisms such as STT and SOT, voltage-assisted writing using electron-mediated voltagecontrolled magnetic anisotropy (VCMA) effect<sup>40</sup> enables lower write energy (~fJ) and smaller cell size due to reduced current, and therefore joule heating and select transistor size.(see Table BC2.1) A VCMA-MTJ is almost the same as an STT-MTJ, except that the tunnel barrier MgO thickness is increased to suppress the tunneling current and enhance the capacitive characteristics of the tunnel barrier.<sup>41</sup> When a voltage is applied across the VCMA-MTJ, charge accumulation or depletion takes place at the FL/barrier interface, leading to a change of electron occupancies among different Fe 3*d* orbitals. Because the interfacial perpendicular magnetic anisotropy (PMA) originates from the Fe 3*d* and O 2*p* orbitals hybridization, this change of electron

occupancy results in the modulation of PMA and thus the energy barrier between the two FL stable states.<sup>40,42,43</sup> The VCMA effect is, therefore, a useful handle to reduce the energy barrier during the write operation, while the energy barrier is restored for retention purposes after writing by simply removing the VCMA bias.

There are two main types of VCMA-assisted magnetization switching schemes. First, removal of the entire energy barrier by the VCMA effect facilitates a precessional motion of the FL along an in-plane bias field direction (built-in or applied). By precise timing of the VCMA pulse width, the FL can switch from one state to the other in half the precession period.<sup>44</sup> Research has shown switching energy of 6 fJ/bit, switching speed of 0.5 ns, write voltage of 1.96 V, current density of 0.3 MA/cm<sup>2</sup> with a WER of 10<sup>-5</sup> using perpendicular MTJs with a VCMA coefficient of 30 fJ/V-m.<sup>45</sup> Another recent work further shows 0.15 ns precessional switching of 120 nm perpendicular VCMA-MTJ at a write voltage of 3.06 V, a current density of 0.3 MA/cm<sup>2</sup> with a WER of <10<sup>-6</sup>.<sup>46</sup> Second, the VCMA effect can be utilized to reduce the write energy in in-plane and perpendicular SOT-MTJs further.<sup>31,47</sup> Research has demonstrated VCMA-assisted (VCMA bias of 1 V) SOT writing of 30 x 80 nm<sup>2</sup> to 50 x 120 nm<sup>2</sup> in-plane MTJ using 2-ns pulse with a current density of 1.2 MA/cm<sup>2</sup> with a high endurance of 10<sup>13</sup> write cycles.<sup>48</sup> Another work shows 5-ns 62  $\mu$ A SOT current writing (VCMA bias of 1.2 V) of 30 x 80 nm<sup>2</sup> in-plane MTJ with WER <10<sup>-8</sup> and endurance over 10<sup>12</sup> cycles, the VCMA coefficient in this device is about 100 fJ/V-m.<sup>49</sup>

The major roadblock of VCMA in either precessional switching or assisting SOT switching is the rather small VCMA coefficient of around 100 fJ/V-m, as defined by the interfacial PMA change under given electric field applied at the MgO barrier.<sup>50</sup> Though ~fJ-level write performance has already been demonstrated, further scaling of MTJs requires higher VCMA coefficient (>300 fJ/V-m) for advanced nodes cache or storage applications.<sup>51</sup> New materials research using Cr and Ir-based crystalline MTJs have shown a high VCMA coefficient of up to 1000 fJ/V-m.<sup>52,53</sup> Meanwhile, detailed chemical and structural characterizations of VCMA-MTJs recently reveal that metal-oxides at the FL/MgO interface lead to large VCMA effect.<sup>54</sup> Another challenge facing VCMA is the longer read time because the thicker MTJ tunnel barrier leads to a much larger MTJ resistance. One way to resolve this is using a large read voltage (V<sub>DD</sub>) which has reverse polarity compared with the write voltage to increase read speed and reduce read disturbance.<sup>55</sup> In terms of the precessional switching scheme, another significant challenge is the non-deterministic nature of the writing process, which results in large WER and narrow write pulse window. The use of pulse shape engineering and reverse biasing can partially help<sup>56,57</sup>, whereas combining VCMA with deterministic writing mechanisms such as type Y SOT<sup>47</sup> and STT<sup>58</sup> may solve this challenge.

# 2.2.2. OXIDE-BASED RESISTIVE MEMORY (OXRAM)

The redox-based nanoionic memory operation is based on a *change in resistance* of a MIM structure caused by ion (cation or anion) migration combined with redox processes involving the electrode material or the insulator material, or both.<sup>59,60,61</sup> Three classes of electrically induced phenomena have been identified that involve chemical effects, i.e., effects which relate to redox processes in the MIM cell. In these three ReRAM classes, there is a competition between thermal and electrochemical driving forces involved in the switching mechanism. Two major types of ReRAM exist: i) those based on metal oxide (OxRAM), which involve oxygen ions/vacancies motion, and ii) conducting bridge-based RAM (CBRAM), which involves metal cation motion. This section covers the three categories of OxRAM, and conducting bridge-based RAM (CBRAM) is covered in the following section. Beyond CMOS has sub-categorized oxide ReRAM (OxRAM) based on the electrical switching type (bipolar versus unipolar) and whether a conductive filament is formed in the device. Most of the literature fits into the three categories: bipolar filamentary, unipolar filamentary, and nonfilamentary.<sup>62</sup>

In most cases, the conduction is of a filamentary nature, and hence a one-time formation process is required before the bipolar switching can be started. If this process can be controlled, memories based on this switching process can be scaled to very small feature sizes. The switching speed is limited by the ion transport. If the active distance over which the anions or cations move is small (in the <10 nm regime) the switching time can be below few nanoseconds, down to sub-nanoseconds range.<sup>63,64</sup> Many of the finer details of the ReRAM switching mechanisms are still under investigation. Developing an understanding of the physical mechanisms governing switching of the redox memory is a key challenge for this technology. Nevertheless, recent experimental demonstrations of scalability,<sup>65</sup> retention,<sup>66</sup> and endurance<sup>67</sup> are encouraging.

#### 2.2.2.1. BIPOLAR-FILAMENTARY OXRAM

Bipolar filamentary OxRAM is the most common form of oxide-based ReRAM. At any given defect density, the number of current paths through the dielectric, in the virgin or fresh state, is proportional to the device area, and consequently the total current is area dependent. In addition, the current magnitude tends to fluctuate from device to device due to randomness of the initial distribution of vacancies/ions. However, cell area dependency is eliminated when the current is dominated by a single conductive path, called conductive filament (CF)). The CF provides an ultimate scaling advantage since it is only limited to the active filament size, which potentially may be as small as a few nm.

A one-time forming process is required for most types of OxRAM devices to create a conduction filament across the dielectric layer linking the electrodes. A stable preferential conduction path is known to form through oxide films subjected to electrical

stress: under the applied voltage, a current abruptly increases at some point in time indicating the occurrence of a dielectric breakdown (BD) resulting in the formation of a CF. During the forming process, electrons injected from the cathode electrode may lead to their trapping at defect sites in the dielectric material inducing chemical bonds breakage and the generation of anion vacancies (Oxygen or Nitrogen).<sup>68,69</sup>

Post-forming switching events between high and low conductive states, which are operated at significantly smaller voltages, are believed to modify the filament conductivity by rupturing/recovering a section of the filament (primarily in the vicinity of the metal electrode) or changing the filament cross-section. The specific mechanisms in filament-type switching depend on the materials (dielectric and metal electrodes) employed in the fabrication of the memory cell and may include more than one type of a conduction mode. The operation of these devices involves redox reactions of the dielectrics sandwiched between two electrodes.<sup>70,71,72</sup> The dielectrics are mostly comprised of one or a few layers of insulating materials<sup>73</sup> (e.g., oxide AlO<sub>x</sub>, HfO<sub>x</sub>, TaO<sub>x</sub>, TiO<sub>x</sub>, WO<sub>x</sub>, ZrO<sub>x</sub>, oxynitrides AlO<sub>x</sub>N<sub>y</sub>, or nitrides including AlN<sub>x</sub> and CuN<sub>x</sub>). TaOx and HfOx are the leading candidates among the aforementioned dielectrics, due to their superior performance (e.g. endurance) and CMOS compatibility.

Since the demonstration of a single crosspoint HfOx device with a 10 nm dimension in  $2011^{74}$ , scaling to a smaller size has been achieved by employing a sidewall electrode in a  $1\times3$  nm<sup>2</sup> cross-sectional HfO<sub>x</sub>-based OxRAM device with reasonable performance in terms of both endurance and retention.<sup>75</sup> Up to  $10^{12}$  cycles has been demonstrated with Zr:SiO<sub>x</sub> sandwiched by graphene oxide layers.<sup>76</sup> Some of the filament-based metal-oxide RRAMs implemented with metal electrodes and a variety of fab-friendly transition-metal-oxides (i.e., HfO<sub>2</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub>, etc.) and nitride devices demonstrated sub-nanosecond,<sup>77,78</sup> switching with high (up to  $10^{12}$  cycles) endurance<sup>79</sup> and retention of more than 10 years. Extrapolated retention at 85°C by stressing TaO<sub>x</sub> in the temperature range from 300°C to 360°C is estimated to be years with an activation energy of 1.6 eV.<sup>80</sup> Reliable switching operations have been demonstrated at 340°C with devices based on 2D layered heterostructures (e.g., graphene/MoS<sub>2-x</sub>O<sub>x</sub>/graphene).<sup>81</sup>

Unconventional electrodes such as graphene have been paired with  $HfO_x$  dielectrics to yield a low power consumption, a write/erase energy of 230 fJ per bit for a single programming transition.<sup>82</sup> Pt/BMO((Bi, Mn)O<sub>x</sub>)/Pt structured OxRAM device was used to demonstrate an even lower write/erase energy per transition, of the order of 3.8 pJ/bit for read and 20 pJ/bit for write operation.<sup>83</sup>

Large scale integration of OxRAM switching based on 1T1R schemes has been carried out by Toshiba, Panasonic and IMEC. In 2013, Toshiba announced the 32 Gb RRAM chip integrated with 24 nm CMOS.<sup>84</sup> In 2014, Panasonic and IMEC demonstrated the encapsulated cell structure with an  $Ir/Ta_2O_5/TaO_x/TaN$  stack on a 2-Mbit chip at the 40 nm node. In addition, passive integration of 1S1R scheme has been reported by Crossbar on a 4-Mbit chip, but the material stack of the OxRAM switch has not been revealed.<sup>85</sup> Ultra-fast (down to 100 ps), compliance-free, low power (< pJ) switching was demonstrated with 1R devices using TiN/HfO2/TiN stack.<sup>86</sup>

A number of technical challenges hampering the commercialization of OxRAM still remain despite the significant advancements made in the field. One of the main challenges is the fact that the switching currents for devices based on the currently most mature materials (e.g.,  $HfO_x$  and  $TaO_x$ ) are still too high (above tens of  $\mu A$ ) for large arrays. Apart from that, the filament formation and rupture processes are stochastic in nature, which leads to variation in switching parameters like the voltage and resistance distribution of the switching. This is especially detrimental to certain applications such as multilevel cell memory.

#### 2.2.2.2. BIPOLAR NON-FILAMENTARY OXRAM

The *Bipolar Non-Filamentary* OxRAM is a non-volatile bipolar resistive switching device composed of one or more oxide layers. One layer is a conductive metal oxide (CMO), which is usually a perovskite such as PrCaMnO3 or Nb:SrTiO<sub>3</sub>.<sup>87</sup> In contrast to *Unipolar* and *Bipolar Filamentary* OxRAM devices – typically based on binary oxides such as TiO<sub>x</sub>, NiO<sub>x</sub>, HfO<sub>x</sub>, TaO<sub>x</sub> or combinations thereof—the resistance change effect of the *Bipolar Non-Filamentary* OxRAM is *uniform*. Depending on the materials choice and structure the current is conducted across the entire electrode area, or at least across the majority of this area. A forming step to create a conductive filament is *not* needed. Non-volatile memory functionality is achieved by the field-driven redistribution of oxygen vacancies close to the contact resulting in a change of the electronic transport properties of the interface (e.g. by modifying the Schottky barrier height). Oxygen can be exchanged between layers due to the exponential increase in ion mobility at high fields. Low current densities, uniform conduction, and bipolar switching imply that substantial self-heating is not involved. Typical R<sub>OFF</sub> to R<sub>ON</sub> ratios are on the order of 10.

One class of the Bipolar Non-Filamentary OxRAM includes a deposited ion conductive tunnel layer (Tunnel ReRAM), e.g. ZrO<sub>2</sub>. Here, a redistribution of oxygen vacancies causes a change of the electronic transport properties of the tunnel barrier. Low current densities and area scaling of device currents enable ultra-high-density memory applications. Set, reset, and read currents scale with device area. In addition, set, reset, and write currents are controlled by the tunnel oxide and hence, can be adjusted by changing the tunnel barrier thickness. Both set and reset IV characteristics are highly nonlinear enabling true 1R cross-point