# INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS<sup>TM</sup>

# 2022 EDITION

# CRYOGENIC ELECTRONICS AND QUANTUM INFORMATION PROCESSING

THE IRDS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# **TABLE OF CONTENTS**

| Ac | knowledgments                                          | viii |

|----|--------------------------------------------------------|------|

| 1. | Introduction 1                                         |      |

|    | 1.1. Summary and Key Points                            |      |

|    | 1.1.1. Superconductor electronics (SCE)                |      |

|    | 1.1.2. Cryogenic semiconductor electronics (Cryo-Semi) | 1    |

|    | 1.1.3. Quantum information processing (QIP)            | 2    |

|    | 1.2. Cross Teams                                       | 2    |

| 2. | Superconductor Electronics (SCE)                       | 3    |

|    | 2.1. Introduction to SCE                               |      |

|    | 2.2. Applications and Market Drivers for SCE           |      |

|    | 2.2.1. Cloud                                           |      |

|    | 2.2.2. Measurement and Calibration Systems             |      |

|    | 2.2.3. Communications                                  |      |

|    | 2.2.4. Quantum Computing: Control and Readout          |      |

|    | 2.3. Present Status for SCE                            |      |

|    | 2.3.1. Logic                                           |      |

|    | 2.3.2. Memory                                          |      |

|    | 2.3.3. Switching Devices                               |      |

|    | 2.3.4. Other Circuit Elements for SCE                  |      |

|    | 2.3.5. Architectures and Applications                  |      |

|    | 2.3.6. Fabrication for SCE                             |      |

|    | 2.3.7. Electronic Design Automation (EDA) for SCE      |      |

|    | 2.3.8. Packaging and Testing for SCE                   |      |

|    | 2.3.9. Interconnects for SCE                           |      |

|    | 2.3.10. Refrigeration                                  |      |

|    | 2.4. Benchmarking and Metrics for SCE                  |      |

|    | 2.4.1. Device and Circuit Benchmarking                 |      |

|    | 2.4.2. Scaling of Devices and Circuits                 |      |

|    | 2.4.3. System and Application Benchmarking             |      |

|    | 2.5. Active Research Questions for SCE                 |      |

|    | 2.6. Roadmaps for SCE                                  |      |

| 3. | Cryogenic Semiconductor Electronics (Cryo-Semi)        |      |

|    | 3.1. Introduction                                      |      |

|    | 3.2. Applications and Market Drivers for Cryo-Semi     |      |

|    | 3.3. Present Status for Cryo-Semi                      |      |

|    | 3.3.1. Transistor Characterization and Modeling        |      |

|    | 3.3.2. Applications ≥ 10 K                             |      |

|    | 3.3.3. Applications < 10 K                             |      |

|    | 3.4. Active Research Questions for Cryo-Semi           |      |

| 4. | Quantum Information Processing (QIP)                   |      |

|    | 4.1. Introduction                                      |      |

|    | 4.1.1. Quantum Computing and Simulation: Introduction  |      |

|    | 4.1.2. Quantum Communication: Introduction             |      |

|    | 4.1.3. Quantum Sensing: Introduction                   |      |

|    | 4.2. Applications and Market Drivers for QIP           |      |

|    | 4.2.1. Optimization                                    | 50   |

|     | 4.2.2.    | Cryptanalysis                                   | 51 |

|-----|-----------|-------------------------------------------------|----|

|     | 4.2.3.    | Quantum Simulation                              |    |

|     | 4.2.4.    | Quantum Machine Learning                        | 51 |

|     | 4.3. P    | resent Status for QIP                           | 52 |

|     | 4.3.1.    | Regional Efforts in QIP                         | 52 |

|     | 4.3.2.    | Analog Quantum Computing: Status                | 53 |

|     | 4.3.3.    | Gate-Based Quantum Computing: Status            | 54 |

|     | 4.3.4.    | Other Gate-Based Quantum Computing: Status      | 58 |

|     | 4.3.5.    | Topological Quantum Computing: Status           | 58 |

|     | 4.3.6.    | Quantum Communication and Sensing: Status       | 59 |

|     | 4.4. B    | enchmarking and Metrics for QIP                 | 60 |

|     | 4.5. A    | ctive Research Questions for QIP                | 61 |

| 5.  | Challeng  | jes                                             | 62 |

| 6.  | Summar    | у                                               | 63 |

|     | 6.1. S    | Superconductor Electronics (SCE)                | 63 |

|     | 6.2. C    | Pryogenic Semiconductor Electronics (Cryo-Semi) | 63 |

|     | 6.3. Q    | Quantum Information Processing (QIP)            | 63 |

| End | dnotes/Re | ferences                                        | 64 |

# **LIST OF FIGURES**

| Figure CEQIP-1 | Josephson Junction Device Structures                               | 3  |

|----------------|--------------------------------------------------------------------|----|

| Figure CEQIP-2 | Gate Set Scaling Trends                                            | 11 |

| Figure CEQIP-3 | Magnetic Memory Device Structures                                  | 17 |

| Figure CEQIP-4 | Superconductor (S) switching devices                               | 19 |

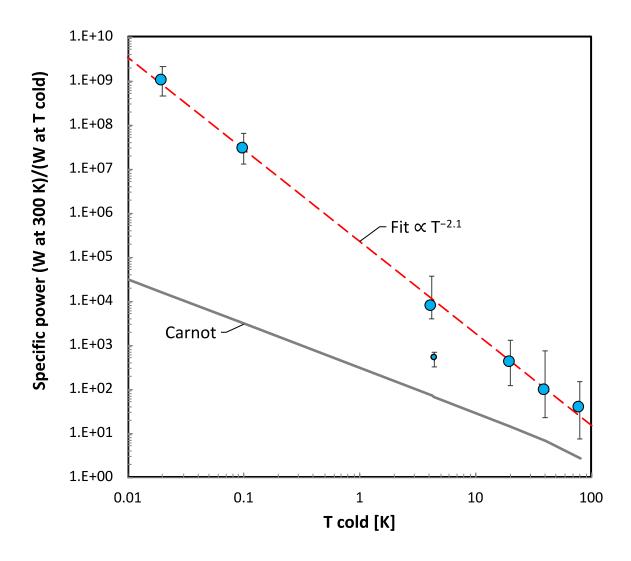

| Figure CEQIP-5 | Specific Power versus Cold Temperature for Cryogenic Refrigeration | 34 |

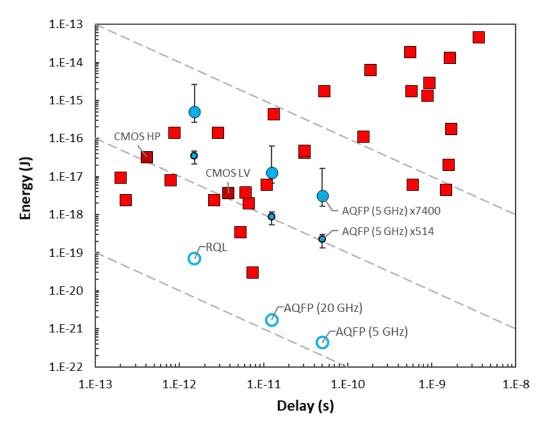

| Figure CEQIP-6 | Energy versus Delay for Intrinsic Elements                         | 36 |

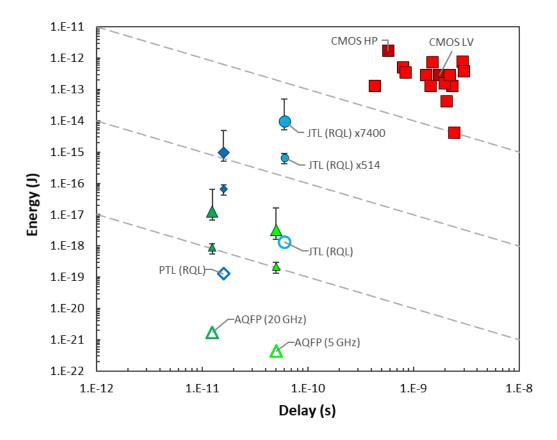

| Figure CEQIP-7 | Energy versus Delay for Interconnects of 1 mm Length               | 37 |

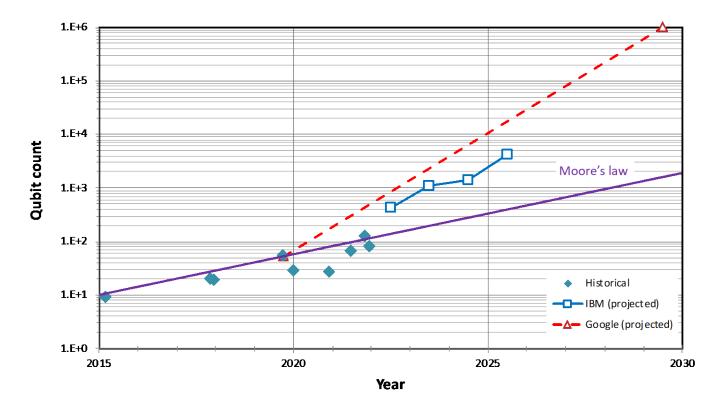

| Figure CEQIP-8 | Superconducting Qubit Trends                                       | 56 |

# **LIST OF TABLES**

| Table CEQIP-1   | Initial Application and Technology Areas Considered for Superconductor Electronics (SCE) | 4   |

|-----------------|------------------------------------------------------------------------------------------|-----|

| Table CEQIP-2   | Matrix of Application or Technology Areas and Market Drivers for SCE                     | 5   |

| Table CEQIP-3   | Typical Sensitivities of SQUID Instruments                                               | 6   |

| Table CEQIP-4   | Superconductor Digital Logic Families                                                    | 10  |

| Table CEQIP-5   | Gate Sets for SCE                                                                        | 11  |

| Table CEQIP-6   | Superconductor Memory Status                                                             | 15  |

| Table CEQIP-7   | Fabrication Processes for SCE                                                            | 24  |

| Table CEQIP-8   | Superconductor Properties for SCE                                                        | 26  |

| Table CEQIP-9   | Superconductor EDA tools                                                                 | 31  |

| Table CEQIP-10  | Specific Power Ranges for Cryogenic Refrigeration                                        | 33  |

| Table CEQIP-11  | Cryogenic Refrigeration Systems for T > 10 K                                             | 33  |

| Table CEQIP-12  | Cryogenic Refrigeration Systems for 1 K < T ≤ 10 K                                       | 33  |

| Table CEQIP-13  | Cryogenic Refrigeration Systems for T ≤ 1 K                                              | 33  |

| Table CEQIP-14  | Energy versus Delay for Intrinsic Elements                                               | 36  |

| Table CEQIP-15  | Energy versus Delay for Interconnects of 1 mm Length                                     | 37  |

| Table CEQIP-15b | Energy versus Delay for Interconnects of 0.01 to 1 mm Length                             | 37  |

| Table CEQIP-16  | Difficult Challenges for SCE                                                             | 38  |

| Table CEQIP-17  | Fabrication Roadmap for Superconductor Electronics (SCE) – Digital Circuits              | 42  |

| Table CEQIP-18  | Fabrication Roadmap for Superconductor Electronics (SCE) — S-MCM                         | 43  |

| Table CEQIP-19  | Interconnect Roadmap for Cryogenic Electronics                                           | 43  |

| Table CEQIP-20  | Matrix of Application Areas and Market Drivers for Cryogenic Semiconductors              | 344 |

| Table CEQIP-21  | Matrix of Application Areas and Market Drivers for Quantum Information Processing (QIP)  | 50  |

| Table CEQIP-22  | Quantum Computing Component Status                                                       | 55  |

| Table CEQIP-23  | Gate-Based Quantum Computing Status Summary                                              | 55  |

| Table CEQIP-24  | Quantum Computing Roadmaps: Superconducting                                              | 56  |

| Table CEQIP-25  | Difficult Challenges for QIP                                                             | 61  |

#### **ACKNOWLEDGMENTS**

This report was prepared by the members of the Cryogenic Electronics and Quantum Information Processing (CEQIP) International Focus Team (IFT).

| Name                   | Area                | Organization                                   |

|------------------------|---------------------|------------------------------------------------|

| Cuthbert, Michael      | Cryo, QIP           | National Quantum Computing Centre, UK          |

| DeBenedictis, Erik     | QIP-QC              | Zettaflops, USA                                |

| Fagaly, Robert L.      | SCE-App             | Honeywell (retired), USA                       |

| Fagas, Giorgios        | QIP                 | Tyndall National Institute, Ireland            |

| Febvre, Pascal         | SCE-Fab             | University Savoie Mont Blanc, France           |

| Fourie, Coenrad        | SCE-EDA             | Stellenbosch University, South Africa          |

| Frank, Michael         | SCE-Logic, -        | Sandia National Laboratories, USA              |

|                        | Roadmap             |                                                |

| Gupta, Deep            | SCE, Cryo-Semi      | SEACORP, USA                                   |

| Herr, Anna             | SCE-Logic, -        | IMEC, Belgium                                  |

|                        | Roadmap             |                                                |

| Holmes, D. Scott       | SCE                 | Booz Allen Hamilton, USA                       |

| [Chair]                |                     |                                                |

| Humble, Travis         | QIP-QC              | Oak Ridge National Laboratory, USA             |

| Leese de Escobar, Anna | SCE-App, SCE-       | Navy NIWC PAC, USA                             |

|                        | Bench               |                                                |

| Mueller, Peter         | QIP-QC              | IBM Zürich, Switzerland                        |

| Mukhanov, Oleg         | QIP-QC, SCE-Logic   | Seeqc, USA                                     |

| Nemoto, Kae            | QIP                 | National Institute of Informatics (NII), Japan |

| Papa Rao, Satyavolu    | SCE-Fab, QIP        | SUNY Polytechnic, USA                          |

| Pelucchi, Emanuele     | QIP-QC              | Tyndall National Institute, Ireland            |

| Plourde, Britton       | QIP                 | Syracuse University, USA                       |

| Soloviev, Igor         | SCE                 | Lomonosov Moscow State University,             |

|                        |                     | Russia                                         |

| Tzimpragos, George     | SCE-Logic, -Metrics | U. of Michigan & UC Santa Barbara, USA         |

| Vogelsang, Thomas      | Cryo-Semi           | Rambus, Inc., USA                              |

| Noboyuki Yoshikawa     | SCE-Logic, -Bench   | Yokohama National University, Japan            |

| You, Lixing            | SCE-Fab             | SIMIT, CAS, China                              |

The team thanks Paolo Gargini, An Chen, Elie Track, and the IEEE Council on Superconductivity for their encouragement and support in developing the CEQIP IFT. We also thank Linda Wilson for administrative help and support.

# CRYOGENIC ELECTRONICS AND QUANTUM INFORMATION PROCESSING

#### 1. Introduction

The goal of this International Roadmap for Devices and Systems (IRDS) chapter is to survey, catalog, and assess the status of technologies in the areas of cryogenic electronics and quantum information processing. Application drivers are identified for sufficiently developed technologies and application needs are mapped as a function of time against projected capabilities to identify challenges requiring research and development effort.

Cryogenic electronics (also referred to as low-temperature electronics or cold electronics) is defined by operation at cryogenic temperatures (below -150 °C or 123.15 K) and includes devices and circuits made from a variety of materials such as insulators, conductors, semiconductors, superconductors, or topological materials. Existing and emerging applications are driving development of novel cryogenic electronic technologies.

Information processing refers to the input, transmission, storage, manipulation or processing, and output of data. Information processing systems to accomplish a specific function, in general, require several different interactive layers of technology. A top-down list of these layers begins with the required application or system function, leading to system architecture, micro- or nano-architecture, circuits, devices, and materials. A fundamental unit of information (e.g., a bit) is represented by a computational state variable, for example, the position of a bead in the ancient abacus calculator or the voltage (or charge) state of a node capacitance in CMOS logic. A binary computational state variable serves as the foundation for von Neumann computational system architectures that dominated conventional computing.

Quantum information processing is different in that it uses qubits, two-state quantum-mechanical systems that can be in coherent superpositions of both states at the same time, which can have computational advantages. Measurement of a qubit in a given basis causes it to collapse to one of the basis states.

Technology categories covered in this report include:

- Superconductor electronics (SCE)

- Cryogenic semiconductor electronics (Cryo-Semi)

- Quantum information processing (QIP)

#### 1.1. SUMMARY AND KEY POINTS

#### 1.1.1. SUPERCONDUCTOR ELECTRONICS (SCE)

- As an emerging technology area with small current market size, important applications and technology areas do not align completely with those considered by the IRDS Application Benchmarking (AB) and Systems and Architectures (SA) teams. Applications and technology areas specific to superconductor electronics were added to improve technology roadmapping ability.

- Large-scale applications exist if the technology can overcome significant challenges.

- Logic approaches are numerous, and none is clearly scalable to larger applications.

- Memory is a weak point with less than 1 MiB currently demonstrated on a single chip.

- Roadmap status: Partial roadmaps are provided.

#### 1.1.2. CRYOGENIC SEMICONDUCTOR ELECTRONICS (CRYO-SEMI)

- Some semiconductor electronic devices and circuits work at cryogenic temperatures without modification. Optimization of performance can require design or fabrication process modifications.

- Markets remain niche and focus on sensors or systems that must operate at cryogenic temperatures.

#### 2 Introduction

- Quantum computing control and readout applications are a current application driver.

- Roadmap status: Not yet ready for roadmaps.

#### 1.1.3. QUANTUM INFORMATION PROCESSING (QIP)

- Emerging technologies with small current markets but large potential.

- Quantum computing is a key area of interest; however, several technical approaches are in competition and none has

emerged as clearly scalable to useful size and capability.

- Roadmap status: Not yet ready for roadmaps, although superconducting quantum computing is close.

#### 1.2. CROSS TEAMS

The Cryogenic Electronics and Quantum Information Processing (CEQIP) team interacts with other IRDS international focus teams.

- Application Benchmarking (AB) and Systems and Architectures (SA) provide applications and system architecture

guidance.

- Outside System Connectivity (OSC) provides insight into system connectivity and interfaces with which systems

covered by CEQIP will need to interact.

- Beyond CMOS (BC) provides insight into novel computation, memory, and communications approaches.

- Packaging and Integration (PI) provides insight into technologies that might be adapted for applications covered by CEQIP.

External organizations that CEQIP interacts with include the IEEE Quantum Initiative and the Quantum Economic Development Consortium (QED-C).

Historical note: In 2017, Cryogenic Electronics appeared as an emerging application within the Beyond CMOS chapter. In 2018, Cryogenic Electronics and Quantum Information Processing became an International Focus Team (IFT) responsible for preparing a separate IRDS chapter.

#### 2.1. Introduction to SCE

Superconductor electronics (SCE) uses circuits and components at least some of which are in the superconducting state. Some materials become superconducting below a critical temperature,  $T_c$ . Critical temperatures of known superconductors range from near absolute zero to about 203 K (-70 °C). The unique physics of superconductors, such as zero dc resistance for sufficiently small currents, allows construction of circuits that are otherwise difficult or impossible to realize. SCE applications tend to cluster in temperatures around the boiling point of liquid nitrogen (77 K, -196 °C), the boiling point of liquid helium (4.2 K, −269 °C), and the superfluid helium-4 temperature range below about 2.17 K.

This report does not seek to explain the operation of superconductor electronic components or circuits except where necessary and consequential to technology roadmapping. Similarly, the focus is on applications that could benefit from technology roadmapping. Following is a very brief introduction. For those seeking to fill in the gaps, open access reviews of superconductor electronics can provide further information [1, 2].

Both passive (linear) and active (nonlinear) superconducting components exist. Examples of passive components are superconducting wires used as inductors, transmission lines, or resonators.

A superconducting loop with inductance L and circulating current I stores magnetic flux  $\Phi = LI$ . Unlike a loop made with normal, resistive material, the current can circulate for as long as it stays superconducting. The behavior is analogous to an ideal capacitor, but the loop stores magnetic flux instead of charge.

Only discrete values of magnetic flux are possible in a superconducting loop due to the quantum nature of the superconducting state. A simple description is that the superconducting state is associated with a wave function and that the superconducting phase change around a loop must be  $2\pi n$ , where n is the number of flux quanta in the loop. The value of the magnetic flux quantum is  $\Phi_0 = 2.07$  fWb. Expressed in practical units, 1 fWb is equivalent to 1 mA·pH or 1 mV·ps. Phase differences between points within superconductor circuits can be produced by magnetic flux, electric currents, and certain devices engineered to exhibit a strongly spatially dependent superconductor wave function. A procedure to determine the flux state in a superconducting loop is described by Fourie [3].

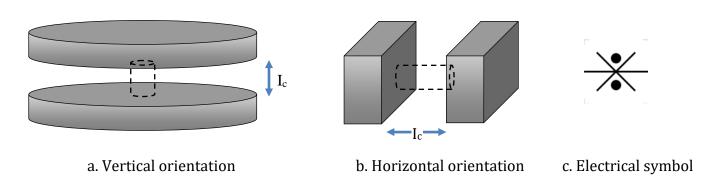

Josephson junctions (JJs) are active superconductor devices used for their nonlinear behavior and switching. Physically, JJs are 2-terminal devices typically made like a thin-film capacitor with superconducting plates or contacts. Common configurations are shown in Figure CEOIP-1. Quantum tunneling of Cooper pairs through the thin barrier layer allows a supercurrent to flow between the contacts with zero voltage drop. The maximum supercurrent is called the critical current,  $I_c$ .

Figure CEQIP-1 Josephson Junction Device Structures

Superconductor electrodes are shown in gray. Contacts to other circuit elements are not shown. The space between the electrodes can be filled with an insulator, semiconductor, or metal. Dashed lines show an optional weak link, which can be made of the same material as the electrodes. Shown is the modern electrical symbol that includes two dots symbolizing a *Cooper pair* [4, 5].

When the current through a critically damped JJ exceeds the critical current, it switches (the superconducting phase difference across the junction jumps by  $2\pi$ ) and produces a single flux quantum (SFQ) output. Note that the time-dependent voltages and

currents produced by the SFQ output depend on the JJ and circuit characteristics, respectively. The switching energy  $E_{sw} \sim I_c \Phi_0$  =  $2 \times 10^{-19}$  J = 0.2 aJ for  $I_c$  = 100  $\mu$ A. Smaller values of critical current  $I_c$  are desirable for energy-efficient applications, within limits due to noise and required bit error rate or ratio (BER) [6].

Single flux quantum (SFQ) digital logic represents digital '1' and '0' by the presence, absence, polarization, or location of magnetic flux quanta within a circuit element. SFQ circuits switch magnetic flux using Josephson junctions and store flux as circulating currents in inductive loops. This is very different from semiconductor circuits, which switch electric charge using transistors and store charge in capacitors. For an explanation of how a simple SFQ gate operates, see [7]. Reviews and books provide further information [1, 8, 9, 10].

Current supplied to SCE circuits is used to both compensate for energy dissipated and to shift superconducting phase differences within the circuit, biasing operation in a desired direction. Supply current type (ac or dc) and magnitude depend on the circuit or logic family. Superconductor phase engineering is an important part of SCE circuit design without analogy in CMOS circuit design [11].

Phase shift elements set or change the superconducting phase  $\varphi$  between locations in a superconducting circuit. Currents through circuit elements can be used to shift the phase. The phase difference across an inductor is given by  $\varphi_L = 2\pi I L/\Phi_0$ , where I is the current, L is the inductance, and  $\Phi_0$  is the magnetic flux quantum. Using an inductor to provide a phase difference involves a tradeoff between current and inductance. Large inductances can require too much circuit area, whereas large dc external currents can become difficult to supply without creating magnetic fields that affect circuit operation. Other devices such as Josephson junctions have different current–phase relationships and present different tradeoffs.

#### 2.2. APPLICATIONS AND MARKET DRIVERS FOR SCE

Few of the application areas and market drivers considered by the IRDS Systems and Architectures (SA) and Application Benchmarking (AB) teams [12, 13] are currently relevant for superconductor electronics. The reason is that cryogenic electronics must continue to serve niche and emerging markets until it can build the capability and capacity to address larger markets.

The initial list of application areas for cryogenic electronics is shown in Table CEQIP-1 along with technology areas specific to superconductor electronics. The SCE-specific technology areas were added to enable initial tracking prior to readiness for applications tracked by the SA and AB teams. The matrix of application and technology areas and market drivers shown in Table CEQIP-2. The example applications and drivers included here are preliminary and require further development. Starting points include a survey of applications and markets for superconductor electronics published in 2010 [14].

Table CEOIP-1 Initial Application and Technology Areas Considered for Superconductor Electronics (SCE)

| Application or technology area | Desired metric                                   | Description                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optimization                   | Solutions per second, feasible problem size      | Integer NP-hard optimization problems                                                                                                                                                                                                                                                                                                                                                      |

| Media processing               | Frames per second                                | Discrete processing, including the filtering, compressing, and decompressing of unknown streaming media                                                                                                                                                                                                                                                                                    |

| Cryptographic codec            | Codons per second                                | Encrypting and decrypting of data at the edge of cryptographic science                                                                                                                                                                                                                                                                                                                     |

| Artificial intelligence        | Accuracy, training and inference time and energy | Graphical dynamic moving image (movie) recognition of a class of targets (e.g., face, car). This can include neuromorphic or deep learning approaches such as DNNs.                                                                                                                                                                                                                        |

| Sensors *                      | Accuracy, resolution, rate                       | Sense physical quantities such as voltage, current, magnetic flux density, or magnetic flux gradient. Example sensors: superconducting quantum interference device (SQUID), superconducting nanowire single photon detector (SNSPD), transition edge sensor (TES), THz superconductor-insulator-superconductor (SIS) and superconducting hot electron bolometer (HEB) heterodyne detectors |

| Sensor array readout *         | Rate, multiplexed inputs                         | Multiplex sensor arrays                                                                                                                                                                                                                                                                                                                                                                    |

| Application or technology area | Desired metric                                                        | Description                                                                                                                                                                                             |

|--------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal processing *            | Digital clock rate, bit depth                                         | Filters, analog to digital conversion (ADC), digital to analog conversion (DAC), digital signal processing (DSP) circuits operating either on streaming digital data or in conjunction with ADC and DAC |

| Digital computing *            | Operations per<br>second, energy per<br>operation, circuit<br>density | Digital computing using superconductor circuits                                                                                                                                                         |

| Quantum computing *            | Coherence time,<br>latency, energy per<br>solution                    | Qubits, interface, error correction, and control circuits for quantum computing                                                                                                                         |

<sup>\*</sup> Technology areas specific to superconductor electronics

Applications can be divided into those that already require cryogenic temperatures for some part of the system and those that do not. Applications already requiring a cryogenic environment provide a much lower barrier of entry for cryogenic electronics. Examples where cryogenic environments are required include: cryogen storage and transport, superconducting magnets such as those in magnetic resonance imaging (MRI) machines and nuclear accelerators, cryogenic devices such as single photon detectors and Josephson junctions, and quantum computing. Note that Josephson junctions are key devices for superconductor electronics, metrology standards, THz detectors in radio astronomy, and for magnetic field sensors and gradiometers based on superconducting quantum interference devices (SQUIDs).

Other applications do not require cryogenic temperatures; however, use of cryogenic electronics can improve metrics such as sensitivity, resolution, or energy efficiency. Examples might include artificial intelligence, discrete event simulation, optimization, and media processing.

Following is further information about the market drivers included in Table CEQIP-2. Roadmaps will be considered to help provide the required technologies when needed by these market drivers.

| Table CEQIP-2 | Matrix of Application of | r Technology Areas and Mark | et Drivers for SCE |

|---------------|--------------------------|-----------------------------|--------------------|

|---------------|--------------------------|-----------------------------|--------------------|

| Application or          | Market Drivers                              |                 |                     |       |                                       |  |  |  |  |

|-------------------------|---------------------------------------------|-----------------|---------------------|-------|---------------------------------------|--|--|--|--|

| technology area         | Measurement<br>and calibration<br>systems * | Digital radio * | Quantum computing * | Cloud | Internet-of-<br>things edge<br>(IoTe) |  |  |  |  |

| Optimization            |                                             |                 |                     | X     |                                       |  |  |  |  |

| Media processing        |                                             | X               |                     |       | X                                     |  |  |  |  |

| Cryptographic codec     |                                             |                 |                     | X     |                                       |  |  |  |  |

| Artificial intelligence |                                             | X               |                     | P     | X                                     |  |  |  |  |

| Sensors *               | G                                           | X               |                     |       |                                       |  |  |  |  |

| Sensor array readout *  | X                                           | X               |                     |       | X                                     |  |  |  |  |

| Signal processing *     | X                                           | G               | X                   |       | X                                     |  |  |  |  |

| Digital computing *     | X                                           | X               | P                   | P     | X                                     |  |  |  |  |

| Quantum computing *     |                                             |                 | G                   |       |                                       |  |  |  |  |

<sup>\*</sup> Technology areas specific to SCE. X: important application; G: critical gating application; P: power-sensitive application.

#### 2.2.1. CLOUD

#### 2.2.1.1. DIGITAL COMPUTING

Large-scale digital computing applications that require many parallel processors for high-performance computing or data centers might benefit from the energy efficiency and other potential benefits of superconductor computing [15]. While the market for digital superconductor computing could be large [7], a necessary first step is to develop small-scale systems and markets. Microprocessor units and memories are currently under development but not yet available as commercial products. Cryptocurrency mining is one application under consideration for superconductor computing as it requires relatively simple processors, limited memory, and energy efficiency [16].

#### 2.2.1.2. ARTIFICIAL INTELLIGENCE (AI)

Artificial intelligence includes applications such as machine learning (ML). The power and energy required to train large machine learning models has been growing and could become an application area for superconductor computing. For current status, see § 2.3.5.4.

#### 2.2.2. MEASUREMENT AND CALIBRATION SYSTEMS

Many of the systems in this section make use of quantum sensing, the use of a quantum system, quantum properties, or quantum phenomena to perform a measurement of a physical quantity [17]. Included is signal processing.

SQUID sensors utilize the Josephson and Meissner effects to create sensors that can detect magnetic flux changes at or below the  $\mu\Phi_0$  level [18, 19, 20]. The use of flux transformers can allow SQUID sensors to detect field changes at the fT level. Additional circuitry can allow SQUID sensors to detect a wide variety of electromagnetic quantities [21, 22]. NanoSQUIDs, which have a flux capture area less than 1  $\mu$ m<sup>2</sup>, have high spatial resolution [20, 23, 24].

| Measurement               | Sensitivity             |

|---------------------------|-------------------------|

| Current                   | 10 <sup>-12</sup> A/√Hz |

| Magnetic flux density     | 10 <sup>-15</sup> T/√Hz |

| dc voltage                | 10 <sup>-14</sup> V     |

| dc resistance             | $10^{\text{-}12}\Omega$ |

| Mutual or self-inductance | 10 <sup>-12</sup> H     |

| Magnetic moment           | 10 <sup>-10</sup> emu   |

Table CEQIP-3 Typical Sensitivities of SQUID Instruments

A SQUID can also be used as a null detector in a cryogenic current comparator (CCC) [25] to achieve part-per-billion current resolution with  $< 0.1 \text{ fA/}\sqrt{\text{Hz}}$  sensitivity. CCCs have applications in voltage standards (§ **2.2.2.2**), quantum Hall effect [26], and in particle accelerator beam diagnostics [27].

Superconducting quantum interference filters (SQUIFs) contain many SQUID loops with different areas in a series-parallel array [28]. SQUIFs have the potential to achieve < 0.1 fT sensitivity levels and have demonstrated > 10 GHz bandwidths [29]. A combination of sub-fT/ $\sqrt{\text{Hz}}$  sensitivity levels and GHz bandwidths may allow SQIFs to be used a wide variety of yet to be discovered applications.

Alternatives to SQUID sensors include the superconducting quantum interference proximity transistor (SQUIPT) [30], and possibly Josephson tunnel junctions incorporating stacked structures of normal metal and ferromagnetic layers [31, 32].

Application frequency ranges vary from roughly  $10^{-4}$  Hz to  $10^{5}$  Hz or higher [19 (Fig. 12)]. While SQUIDs can be made from either low temperature or high temperature superconductors (LTS, HTS), only LTS SQUIDs are enough sensitive to cover all applications. The bandwidth of commercially available electronics is typically dc to 100 kHz with flat frequency and flat phase response. Bandwidths of 10 MHz can be achieved by operating in an open loop configuration where the maximum signal does not exceed  $\Phi_0/2$ .

While laboratory applications of SQUIDs have been the springboard for significant commercial successes in the areas of biomagnetism, magnetic property measurement systems, and geophysics, the commercial market for laboratory systems is

typically at the 2 to 3 million USD level [33]. One potential use of SQUIDs with a significant commercial application is in the detection of low-field MRI signals [34].

Photon detectors such as superconducting nanowire single photon detectors (SNSPDs) have applications in quantum optics and quantum communication, primarily because of their low timing jitter and capability to detect individual low-energy photons with high quantum efficiency [35, 36, 37]. Josephson junctions can also function as single photon detectors [38].

#### 2.2.2.1. BIOMAGNETISM AND MEDICAL MEASUREMENTS

The sensitivity of SQUIDs has allowed non-invasive measurements of electrophysiological activity that has led to the development of number of medical instruments [21]. The major use, responsible for over half a billion USD in sales to date, has been magnetoencephalography (MEG) for magnetic source imaging (e.g., focal epilepsy regions). Another area where SQUID-based methodologies offer diagnostic capabilities is magnetocardiography (MCG), particularly in fetal MCG to diagnose fetal heart rhythm abnormalities. Other uses of SQUID biomagnetometers include magnetoenterography (measurements of the stomach and intestines), magnetopneumography (magnetic remnance measurements of the lung), and magnetomyography and magnetoneurography (muscle and peripheral nerve studies). One disadvantage of ultra-sensitive SQUID biomagnetometers is the need for magnetically shielded rooms to reduce the effects of external electromagnetic noise.

The major drivers in the adoption of medical instrumentation are clinical acceptance, cost and safety. Clinical acceptance requires the demonstration of superior, rather than incremental, diagnostic capabilities in a modality that the physician can easily interpret. Medical equipment costing above 1 million USD is limited to medium to large hospitals. When instrument prices drop to the 250,000 USD level, the potential market expands to small hospital and medium to large clinics. Currently the per channel cost for high channel count SQUID biomagnetometers (e.g., MEG) is at or above a few thousand USD. Significant reductions in per channel cost or eliminating the need for expensive magnetically shielded rooms could significantly increase the market for SQUID biomagnetometers.

Improvements in high-temperature SQUID sensors, which are currently more expensive than low-temperature SQUID sensors, could also reduce the cryogenic requirements with a subsequent reduction in system cost.

#### 2.2.2.2. VOLTAGE STANDARDS

Voltage standard systems based on superconducting Josephson junction arrays became commercially available in 1996 and have continued development [39, 40]. An economic impact assessment of NIST's Josephson volt program performed in 2001 found a net present value of 45 million USD in the year 2000 [41]. At least 16 Josephson voltage standard systems were in operation in the United States at that time. Current information is needed about markets and market drivers for voltage standard systems.

Two complementary types of Josephson voltage standards used today are the programmable Josephson voltage standard (PJVS) and the Josephson arbitrary waveform synthesizer (JAWS, also known as the ac Josephson voltage standard or ACJVS) [40]. The main dc application for PJVS systems is the direct calibration of secondary voltage standards. With the 2019 redefinition of base units in the International System of Units (SI), both PJVS and JAWS systems will become key components for the direct realization of the unit volt.

The push to improve ac voltage standards is presently a driver for cryogenic circuit development [42, 43]. One reason is that the output voltage of a JAWS is limited by the number of Josephson junctions (JJs) that can be driven by a single pulse-generator channel. In one paper [43] the number of JJs driven by one generator channel was doubled to 51,200.

#### 2.2.2.3. MAGNETIC PROPERTY MEASUREMENT SYSTEMS

Since the discovery of high-temperature superconductors, SQUID based susceptometers have been a mainstay in magnetic property measurements. Gradient detection coils surround the sample region of a variable temperature (typically 1.8 to 400+K) insert. Surrounding the detection coils is a moderately high-homogeneity (100 ppm) superconducting magnet (0 to 9 T). The sample is moved inside the detection coils, and the resulting changes in flux are used to calculate the magnetic moment of the sample. Some systems have both axial and transverse coils. AC susceptibility can be measured by adding ac coils, although the applied fields are much smaller ( $\mu$ T). The dynamic range can vary from  $10^{-8}$  to 2 emu. To date, over 1,300 SQUID susceptometers (from all suppliers) have been delivered generating over 250 million USD in revenues. Commercially available since the late 1970s, this market segment is the premier example that needed a SQUID-based product in quantity. Commercial manufacturers include Quantum Design and Cryogenic, Ltd.

The variable temperature platform can be expanded (without SQUID detection coils) to a variable temperature physical property measurement system allowing a wide variety of measurements to be taken from 50 mK to 800 K in fields exceeding 14 T. The variable temperature susceptometer concept can be converted to remnant field geophysical measurements (§ 2.2.2.5)

by removing the dc superconducting magnet and placing three orthogonal detection coils in a magnetically shielded region. Typically placed in a horizontal orientation, nearly 150 systems have been delivered generating nearly 30 million USD in revenues. Commercial manufacturers include 2-G Enterprises and Tristan Technologies.

Nondestructive evaluation (NDE) systems using SQUID sensors have been reviewed by [44].

#### 2.2.2.4. MICROSCOPY

Microscopes with SQUID or magnetic tunnel junction sensors image surface magnetic flux density with micrometer-scale resolution [45, 46, 47, 48]. Recent developments include a vector-scanning SQUID microscope [49, 50] and a system for investigation of geological samples [51]. Commercial manufacturers include Neocera Magma [52] and Tristan Technologies [53].

#### 2.2.2.5. GEOPHYSICS

Magnetic field gradiometers are used to prospect for magnetic ores [21]. The value of ore deposits discovered is reported to be several billion USD, however, the cost of the cryogenic electronics is a tiny fraction of that amount. These systems require only a few Josephson junctions and can use high-temperature superconductors operating at liquid nitrogen temperatures (~77 K). A survey of applications affecting the environment found additional applications such as the detection of unexploded ordinance (UXO) [54].

#### 2.2.2.6. ASTRONOMY

Radio and Infrared Astronomy has played an essential historical role in superconductor electronics by pulling the developments of sensitive quantum-limited superconducting SIS and HEB heterodyne detectors for millimeter, then submillimeter/THz radio telescopes and infrared telescopes like the Herschel Space Observatory or the Planck satellite. Some astronomy applications using cryogenic sensor arrays [55, 56] are growing in array size to the point that multiplexing and signal processing is needed close to the sensors. The need to go from single pixel detection at THz frequencies to array sensors with thousands or more pixels also exists for THz detectors but suffers currently from technological limitations of back-end processing.

#### 2.2.3. COMMUNICATIONS

Developed communications applications are covered in the following sub-sections. Proposed communication applications include chaos encryption using a circuit with a Josephson junction in parallel with a memristor [57].

#### 2.2.3.1. WIRELESS COMMUNICATIONS

High-temperature superconductor (HTS) filters are used in wireless base stations to increase base station coverage area and data throughput. Superconductor Technologies Inc. has products that operate in over 10,000 base stations [58].

#### 2.2.3.2. DIGITAL RADIO

Software-defined radios perform signal processing entirely in the digital domain. By contrast, traditional radios perform signal processing in the analog domain at a single frequency. Software-defined radios require both ultra-high-speed analog-to-digital converters (ADCs) and equally fast digital signal processing (DSP) of the converted signals, but do not require much memory. ADC and DSP circuits based on superconductor electronics have been demonstrated at speeds up to 40 GHz [59]. The commercial digital-RF receiver manufactured by HYPRES [60] performs ADC and DSP using superconductor electronics [61]. The superconducting components operate at about 4 K with a fully automated and cryogen-free refrigeration system. The application space extends beyond communications to many other uses of the radio frequency spectrum for surveillance, navigation, and spectrum management.

#### 2.2.4. QUANTUM COMPUTING: CONTROL AND READOUT

Quantum computing systems operating at cryogenic temperatures below 10 K can benefit from local control and readout. Advantages include less energy dissipation in the cryogenic space and faster response times for control. Overviews of the needs are given in [744, 777, 793, 815]. The need for superconductor electronic control and readout is expected to grow with the scale of the quantum computer supported. The need for superconductors increases for systems requiring temperatures in the millikelvin range and decreases greatly for systems not requiring temperatures below about 10 K.

Current status is covered in section 2.3.5.5 and related applications of cryogenic CMOS are covered in section 3.3.3.2.

#### 2.3. PRESENT STATUS FOR SCE

The integrated circuit chip with the largest Josephson junction count is the 2020 D-Wave Pegasus P16 quantum annealing processor with 1,030,000 Josephson junctions [62, 746, 747]. Considering that state-of-the-art CMOS wafer-scale chips are available with more than a trillion transistors [63], superconductor electronics is still far behind the semiconductor industry in key metrics such as integrated circuit density and complexity. Prospects remain for higher operating speeds and improved energy efficiency, especially for applications requiring operation at cryogenic temperatures.

#### 2.3.1. LOGIC

Several SCE digital logic families and some important characteristics are summarized in Table CEQIP-4 and further described in subsections below. Characteristics include:

- SFQ count per logical '1' or per time interval: Most of the logic families transfer one or more single flux quanta (SFO) to communicate state values between gates. By contrast, quantum flux parametrons (OFP) use currents between gates.

- Power type: DC or AC.

- Static power: Qualitative indicator of static power dissipation.

- **Dynamic power per switch**: Power dissipated per switching device operating at frequency f.

- **Transformers:** P for power transformer usage and G for logic gate transformer usage.

- Clocked gates: Use of logic gates that require clocking. Logic depth is defined as the maximum number of logic operations between two subsequent clocked resources, such as a DFF in CMOS or any logic gate in RSFQ. Logic families with only clocked (synchronous) gates are limited to a logic depth of one, whereas unclocked (asynchronous) gates allow greater logic depths.

- JJ count  $log_{10}(n)$ : Josephson junction or switching device count n in largest circuit demonstrated and displayed as  $log_{10}(n)$ . Values in parenthesis () are designs only.

To be identified are additional parameters for future logic family monitoring and comparison. Candidates include average number of junctions or other resources per logic gate (e.g., area, number of layers), energy per operation, or overhead for clock and power supply.

Table CEQIP-4 Superconductor Digital Logic Families

| Name                                    | Section<br>§                       | $\widetilde{S}FQ$ | Power | Static<br>Power | Dynamic power per switch                | Trans-<br>formers | Clocked<br>Gates | $JJ count log_{10}(n)$ |

|-----------------------------------------|------------------------------------|-------------------|-------|-----------------|-----------------------------------------|-------------------|------------------|------------------------|

| RSFQ: rapid single flux quantum         | 2.3.1.1                            | 1                 | – DC  | High            | $lphaI_carPhi_0 f$                      | 1                 | Yes              | 4.4                    |

| LR-RSFQ: inductor-resistor RSFQ         | 2.3.1.1                            | 1                 | - DC  | Low             | $lphaI_carPhi_0 f$                      | -                 | Yes              | 1.6                    |

| LV-RSFQ: low-voltage RSFQ               | 2.3.1.1                            | 1                 | - DC  | Low             | $lphaI_c{\Phi_{\!0}} f$                 | -                 | Yes              | 3.7                    |

| ERSFQ: energy-efficient RSFQ            | 2.3.1.2                            | 1                 | - DC  | 0 *             | $I_b \Phi_0 f$                          | -                 | Yes              | 3.8                    |

| eSFQ: efficient SFQ                     | 2.3.1.2                            | 1                 | - DC  | 0 *             | $I_b \Phi_0 f$                          | -                 | Yes              | 3.4                    |

| Self-timed SFQ                          | Error! Reference source not found. | 1                 | – DC  |                 |                                         |                   |                  | 2.8                    |

| DSFQ: dynamic SFQ                       | 2.3.1.4                            | 1                 | - DC  | ‡               | ‡                                       | -                 | Some             | 0.7                    |

| TSFQ: temporal SFQ                      | 2.3.1.5                            | 1                 | - DC  |                 |                                         | -                 | No               | (2.8)                  |

| xSFQ: alternating SFQ                   | 2.3.1.6                            | 2                 | - DC  | ‡               | ‡                                       | -                 | No               |                        |

| nTron: nanowire cryotron                | 2.3.1.7                            | 1                 | - DC  | ~0              | varies                                  | -                 | Yes              | 1.5                    |

| hTron: heater-cryotron nanowire         | 2.3.1.7                            | 1                 | - DC  | ~0              | varies                                  | -                 | Yes              | 1.2                    |

| HFQ: half flux quantum                  | 2.3.1.8                            | 0.5               | - DC  | Low             |                                         | -                 | Yes              | 1.2                    |

| SFQ-AC: AC-powered SFQ                  | 2.3.1.9                            | 1                 | ~ AC  | ‡               | ‡                                       | P                 | Yes              | 5.9                    |

| RQL: reciprocal quantum logic           | 2.3.1.10                           | 2                 | ~ AC  | ~0              | $\alpha I_c \Phi_0 f 2/3$               | P, G              | Some             | 4.9                    |

| PML: phase mode logic                   | 2.3.1.10                           | 1                 | ~ AC  | ~0              | $\alpha I_c \Phi_0 f/3$                 | P, G              | Some             |                        |

| AQFP: adiabatic quantum flux parametron | 2.3.1.11                           | -                 | ~ AC  | ~0              | $\alpha I_c \Phi_0 2f \tau_{sw}/\tau_x$ | P, G              | Yes              | 4.3                    |

| RQFP: reversible QFP                    | 2.3.1.12                           | -                 | ~ AC  | ~0              | $\alpha I_c \Phi_0 2f \tau_{sw}/\tau_x$ | P, G              | Yes              | 1.4                    |

SFQ: count per logical '1'; JJ count: Josephson junction or switching device count in largest circuit demonstrated as  $\log_{10}(n)$ ;  $\alpha$ : activity factor (fraction of JJs that switch in a clock cycle);  $I_c$ : average critical current;  $I_b$ : bias current;  $\tau_{sv}$ : intrinsic switching time;  $\tau_x$ : excitation rise/fall time; \*: for  $I_b$  within the energy-efficient range; ‡ depends on whether powered like RSFQ or ERSFQ, with some additional loss in reset resistors

Gate set scaling trends are tracked in Table CEQIP-5. This report includes AQFP (MAJ+INV) and CMOS (NAND2) gate sets.

Figure CEQIP-2 Gate Set Scaling Trends

Note: The difference in gate set areas was a factor of about 25,000 in 2020 and about 60 when comparing gate sets at an equivalent feature size of 350 nm.

#### Table CEQIP-5 Gate Sets for SCE

#### 2.3.1.1. RSFQ, LR-RSFQ, LV-RSFQ Logic

Single flux quantum (SFQ) digital logic was introduced in section 2.1. Ordinary SFQ logic gates behave like state machines and require a clock signal to both logically evaluate and reset the gate. Such explicit use of clock signals in logic networks creates significant challenges with the application of the register transfer level (RTL) design paradigm, a cornerstone of VLSI digital design methodology. RTL subdivides large digital circuits into clocked registers and clock-free, state-free logic networks called combinational logic clouds. Specialized tools are required when most logic gates require clocking.

**RSFQ**: Rapid single flux quantum circuits use resistors to distribute dc supply currents (power) [64]. While the use of resistors simplifies superconducting circuit design and provides steady current supply, the static power dissipated is typically between 10 and 100 times the dynamic power [65].

Status: Several large-scale RSFQ integrated circuits have been demonstrated at high clock frequencies around 50 GHz, which include 8-bit microprocessors with memory [66, 67], single-precision floating-point units [68], FFT processors [69], and reconfigurable data paths [70]. An 8-bit ALU fabricated using the Nb 9-layer,  $100 \,\mu\text{A}/\mu\text{m}^2$  process had a computational efficiency of 40 TOPS/W [71]. An 8x8 bit multiplier with 20,251 JJs operated up to 48 GHz [72]. An 8-bit-wide, bit-parallel datapath composed of an arithmetic logic unit and register files operated up to 64 GHz [73].

**LR-RSFQ**: Inductor-resistor (LR) SFQ can reduce static power consumption to the same order as the dynamic power consumption through optimization of the circuit parameters in the current supply network [74, 75].

**LV-RSFQ**: Low-voltage operation of RSFQ circuits can improve energy efficiency [6, 76, 77] and can be implemented without shunt resistors for further energy and area savings [78]. An 8-bit ALU has been demonstrated at 30 GHz with energy

efficiency greater than 100 TOp/J [79]. A bit-parallel multiplier operated at 54 GHz [80]. Shift register operation at 83 GHz clock frequency was demonstrated using a 200 μA/μm<sup>2</sup> JJ process [81].

#### 2.3.1.2. ERSFQ, ESFQ LOGIC

**ERSFQ**: Energy efficient RSFQ gates are similar to those in RSFQ, which reduces the work required to switch between these logic families. The main difference is that dc supply current (power) is distributed using a current-limiting Josephson junction in series with a large bias inductor as well as a clocked feeding Josephson transmission line (FJTL) to maintain adequate bias voltage and current stability [10, 65, 82, 83, 84]. Power distribution for energy-efficient operation adds about 30% to ERSFQ circuit area [85].

Status: ERSFQ has been used to make 8-bit parallel adders with 560 and 1360 JJs [86], a decoder for RAM [87], an 8-bit ALU [88], and fast parallel counters [89]. Proposed is a superconducting magnetic FPGA based on ERSFQ logic [90].

**eSFQ**: Efficient SFQ biasing networks are designed so that in each clock period the superconducting phase at all bias injection points goes through the same change [65, 91, 92]. Smaller bias inductors are required than for ERSFQ, however the gates must be designed differently, which limits compatibility with and reuse of RSFQ circuit designs.

Status: Demonstrations of eSFQ include asynchronous [93, 94] and wave-pipelined circuits [92]. The largest eSFQ circuit demonstrated is a 4 bit ALU with 2,569 JJs [94].

#### 2.3.1.3. SELF-TIMED SFQ

In the above-described SFQ approaches, logic gates are clocked. Traditionally, a clock tree is used to route a clock signal to each gate. Self-timing schemes, in which the clock is locally generated by the incoming data pulses, are a way to avoid clock trees without requiring development of clock-free gates. Proposed self-timing approaches include Data-Driven Self Timed (DDST) RSFQ, Dual-Rail RSFQ (DRRSFQ), RSFQ Asynchronous Timing (RSFQ-AT), and Delay Insensitive Dual-Rail (DI) RSFQ [95]. Demonstrated circuits include asynchronous eSFQ toggle flip-flops [93] and dual-rail eSFQ [94]. Proposed applications include asynchronous clock distribution networks [96].

Another way to eliminate clocking, this time without the need to create explicit clock, is by repurposing existing cells. This repurposing may happen by routing one of the data inputs to the clock port of the synchronous components. One such case is the recently proposed "clockless" RSFQ approach, where synchronous NDRO cells and delay elements are used to realize AND and NIMPLY functions [97]. These functions have been used in conjunction with synchronous components to construct a 4-bit carry look-ahead adder (CLA) and a 32-bit arithmetic logic unit (ALU) [98]. Note that although a clock signal may no longer be needed, the resulting system is prone to metastability and requires careful attention to timing.

#### 2.3.1.4. DYNAMIC SFQ

**DSFQ**: Dynamic SFQ gates self reset using a nonlinear resistive leakage circuit that allows the usable hold time to be a large fraction of the self-reset time [99, 100]. For clocked SFQ gates, the clock signal both logically evaluates and resets the gate. The self-timed approaches presented in 2.3.1.3 avoid using a clock for gate evaluation but use just one of the inputs to reset, which leads to a risk of metastability. DSFQ gate inputs are functionally equivalent, which minimizes timing concerns. Additional benefits could come from DSFQ majority gates [101]. A challenge is that self-reset times can be sensitive to fabrication variations, especially for longer reset times. Partial path balancing can provide benefits without the need for longer self-reset times [102].

#### 2.3.1.5. TEMPORAL SFQ (TSFQ)

Computational temporal logic represents information in the time domain, for example as time between pulses or as delay lengths. A set of basic temporal logic operations—First Arrival, Last Arrival, Delay, and Inhibit—replaces Boolean logic operations such as OR, AND, and NOT [103, 104]. These temporal logic operators do not use binary inputs so there is no need to translate the presence or absence of data pulses to True or False statements as in Boolean logic. A consequence is that no clocking is required at the gate level. Resetting of TSFQ logic gates is required and can be performed using the same leakage techniques as in DSFQ. The set of temporal logic operators is functionally complete over natural numbers [105]. In other words, any arbitrary function that operates over non-negative integers is implementable.

#### 2.3.1.6. ALTERNATING SFQ (xSFQ)

**xSFQ**: Alternating SFQ leverages a duality between Boolean and temporal operators to repurpose the asynchronous First Arrival and Last Arrival TSFQ cells to realize Boolean OR and AND functions [106]. To achieve completeness, xSFQ relies on the theory of unordered codes, such as dual-rail codes, under which AND and OR alone are sufficient. To eliminate the need for external signals or leakage mechanisms for resetting, an alternating encoding is used. Clock-free combinational logic elements

are sandwiched between banks of storage elements. Potential advantages include significant reductions in clock networks and greater ability to use EDA tools developed for conventional CMOS circuits.

#### 2.3.1.7. NANO-CRYOTRON LOGIC

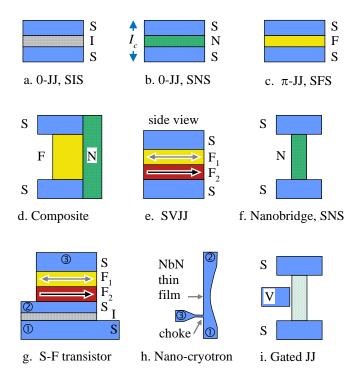

Nano-cryotrons are multi-terminal devices, typically with three or four terminals. For device structure, see Figure CEQIP-4h. Logic based on nano-cryotrons is under active development [107, 108, 109, 110, 111, 112, 113, 114].

#### 2.3.1.8. HFQ: HALF FLUX QUANTUM LOGIC

Half flux quantum circuits produce, transfer, and store half flux quanta [115]. Recall that single flux quantum (SFQ) circuits use Josephson junctions called 0-JJs with a current-phase relationship  $I = I_C \sin(\varphi)$ . HFQ circuits can be constructed from combinations of 0-JJs and either pi-JJs or  $2\varphi$ -JJs. Pi-JJs have a current-phase relationship  $I = I_C \sin(\varphi - \pi) = -I_C \sin(\varphi)$  and  $2\varphi$ -JJs have a current-phase relationship  $I = I_C \sin(2\varphi)$ . HFQ circuits require little additional inductance, so should have scaling advantages [116, 117, 118].

LV-HFQ: Low-voltage, half flux quantum circuits incorporate pi-JJs in LV-RSFQ circuits and are expected to further improve energy efficiency, circuit density, and operating margins [115].

Interfaces between SFQ and HFQ circuits have been demonstrated [119].

#### 2.3.1.9. SFQ-AC

AC-powered SFQ uses transformers in series to provide current to cells. Cells using AC bias require only a transformer; however, transformers do not scale well at feature sizes much below 1 µm. Cells requiring DC bias can be supplied by AC/DC converters [120, 121] or AC/SFQ converters [122]. Both AC/DC and AC/SFQ converters require additional circuit overhead. For best energy efficiency, the AC frequency should be greater than the clock frequency of the DC cells. Current supply to the chip can be decreased by a factor roughly equal to the biased cell count divided by the number of parallel AC supply lines on the chip.

SFQ-AC works best when most cells use AC or no bias current. A challenge is that few such cells exist, so more need to be developed.

#### 2.3.1.10. RQL AND PML

Reciprocal quantum logic (RQL) [123, 124, 125] and phase mode logic (PML) [126] are related logic families. RQL encodes a digital 1 using two flux quanta of opposite sense and corresponds to wave pipeline operation. PML encodes digital data as high and low states of the superconducting phase, which dissipates less dynamic power. Both use energy-efficient ac resonator-based distribution for power and clock signals. The power is applied in parallel providing scalability to VLSI. Resonators also provide clock stability with zero jitter and skew. Both RQL and PML include combinational gates that allow 12 levels of logic per pipeline stage at 10 GHz. RQL and PML logic provide component-efficient superconducting gates with the same number of junctions as transistors in CMOS gates as well as full compatibility with standard RTL based synthesis design flow. Advantages include low error rates as the effective critical current of Josephson junctions in distributed networks of comparator-free RQL logic is about three times that of a single junction [127].

Design achievements include tile-based physical design to facilitate automated layout, mitigation of flux trapping, and a resonant clock network for chip-level power distribution with 50% power efficiency. A complete RTL-to-GDSII automated design flow has been developed and used to design a 16-bit CPU [128]. Circuit demonstrations include individual logic gates with a 7 dB clock margin; 3.5 GHz resonator powering a shift register with 72,800 JJs and 4 dB clock margin [129]; 16-bit ALU and 16-bit register file [130]; 0.25 MJJ resonator-based yield vehicle; and an 8-bit CPU with fully functional debug logic, register file, 8-bit CLA, and performance of write and read memory instructions [131].

#### 2.3.1.11. QFP: QUANTUM FLUX PARAMETRON LOGIC

Adiabatic quantum flux parametron (AQFP) logic achieves extremely high energy efficiency by changing the potential shape adiabatically between double-well and single-well during switching [10, 132, 133]. Unlike SFQ logic families, current polarity and magnitude communicate state values between gates. Other distinguishing features include the use of AC power and current transformers. The typical switching energy is about  $4.3 \times 10^{-22}$  J at 5 GHz clock frequency assuming unshunted junctions with critical current density of  $100 \,\mu\text{A}/\mu\text{m}^2$  [134]. Determining the energy dissipation of an AQFP logic gate requires accounting for the data-dependent interactions between the gate and its environment [135]. The switching energy can be further decreased in proportion to the clock frequency and perhaps even below the Landauer thermal limit by using reversible quantum-flux-parametron (RQFP) gates (§ 2.3.1.12).

Operation at high frequencies with low bit energy and low bit error rate or ratio (BER) was confirmed experimentally [136, 137]. Multi-excitation circuits (ME-AQFP) can multiply the excitation current frequency, which typically has a maximum of about 5 GHz, by a factor of 2 or 4 to allow AQFP circuit operation up to about 20 GHz [138]. AQFP logic circuits are typically clocked by four-phase AC clocks; therefore, the logic depth per clock cycle is four. Delay-line clocking can increase both the number of phases and logic depth, possibly exceeding a clock depth of 20 for a 5 GHz clock frequency and 100 µA/µm² junction process [139, 140, 141]. Other low-latency excitation schemes have been proposed based on microwave power dividers [142] and n-phase clocking [143].

Digital logic AQFP circuit design uses a standard cell design approach with similarities to CMOS circuit design [144]. An AQFP NAND gate requires 6 junctions, whereas the corresponding CMOS gate uses 4 transistors. Transformers for supply and signal currents also add area and are difficult to scale to small sizes. Because a majority gate is a fundamental logic gate in AQFP logic, majority-based logic synthesis is desirable [145]. Several circuits have been designed and demonstrated by using an automated top-down design flow, which includes logic synthesis, and placement and routing [146, 147]. Functional operation has been demonstrated for 8-bit carry-lookahead (CLA) adders [148, 149] and 16-word, 1-bit register files [150]. An 8-bit CLA was demonstrated with energy dissipation of only 1.5 aJ per operation, or  $24k_BT$  per junction switching [151]. The demonstrated MANA 4-bit AQFP microprocessor with 21,460 junctions is estimated to dissipate about 30 aJ/op at 5 GHz [152].

Directly coupled quantum-flux-parametron (DQFP) is an adiabatic superconductor logic that does not require signal transformers [153, 154]. While AC power transformers are still required, the nearly 40% reduction in gate area is significant. AQFP with  $\pi$  Josephson junctions also can operate without using signal transformers [155].

#### 2.3.1.12. REVERSIBLE LOGIC STYLES

There has been a long history of efforts to develop superconducting logic styles capable of approaching (logically and physically) reversible computation, starting with Likharev's work on parametric quantrons (PQ) in the 1970s [156], and reversible versions of the original 1987 quantum flux parametron (QFP) of Goto  $et\ al.$  [157]. These early efforts relied on adiabatic transformation of the potential energy function in one or more coupled SQUID loops, a theme which continues today in the recent work on negative mutual-inductance SQUIDs (nSQUIDs) [158, 159] and on reversible quantum flux parametron (RQFP) logic [160, 161, 162, 163, 164, 165], a variation on AQFP logic. In addition, several groups have investigated alternative *ballistic* styles of superconducting reversible logic, including groups in Hokkaido in 2008 [166, 167], Northrop Grumman in 2010 [168], the University of Maryland, [169, 170], and Sandia National Laboratories [171, 172, 173]. These efforts aim to surpass the energy efficiency of the existing irreversible logic styles such as those in Table CEQIP-4 and can potentially eventually push beyond the Landauer limit of  $\sim kT$  energy dissipation per operation that applies to irreversible logic.

#### 2.3.1.13. QUANTUM PHASE-SLIP JUNCTION (QPSJ) LOGIC

Quantum phase slip junctions (QPSJ) are superconductor nanowire devices with a nonlinear I-V characteristic. QPSJs are a dual to Josephson junction devices, with the roles of phase and charge interchanged as well as current and voltage [174, 175, 176, 177, 178, 179, 180, 181, 182]. Adiabatic logic circuits based on quantum charge parametrons could be made from QPSJs [183]. Needed is demonstration of QPSJ-based circuits with at least 100 junctions to allow evaluation of their viability for complex applications.

#### 2.3.1.14. OTHER SCE LOGIC

Spintronic superconductor electronics is a new field since about the year 2000. Like traditional spintronics, the approach is to utilize spin currents for information processing. Contrary to charge current, spin current does not conserve and is not always accompanied by charge transfer, so might be more energy efficient. Reviews of superconductor spintronics include [184, 185, 186, 187, 188]. This new field is at the stage of development and demonstration of device concepts rather than production. It is not easy to produce spin superconducting currents; however, when produced, they persist in superconductors much better in both equilibrium [189] and nonequilibrium transport [190, 191, 192]. The use of spin currents to switch memory devices is covered in § 2.3.2.2.

Other superconductor logic families include those based on Josephson junction oscillators [193], and control of magnetic flux quanta using magnetic fields [194].

#### 2.3.2. **MEMORY**

Superconductor electronic memory can be classified by memory device technology: 1) Josephson junction logic circuits, 2) magnetic devices, or 3) nanowire superconductor devices; and by use: (a) register, (b) cache, or (c) main memory.

The magnetic flux in a superconducting loop in steady state is quantized and thus can be used to provide the physical basis for a digital memory element. The absence or presence of a flux quantum in the loop represents binary '0' or '1'. Superconducting memory cells have one or more Josephson junctions or nanowire superconductor devices in the loop to control and sense the number or location of flux quanta present.

For reviews, see [9 § "16.7 Memory for Cryogenic Supercomputer", 195, 196].

|                                                    |             | ı        | Bit Cell Area |       | Latency [ns] |      | y [fJ] | Static |         |

|----------------------------------------------------|-------------|----------|---------------|-------|--------------|------|--------|--------|---------|

| Name                                               | References  | RAM      | [µm²]         | Read  | Write        | Read | Write  | Power  | Bits    |

| SR: shift register, ac-biased                      | [121]       |          | 300 (15×20)   |       |              |      |        |        | 202 280 |

| SR: shift register                                 | [339]       |          |               | 0.02  | 0.02         | 0.1  | 0.1    | 0.2 mW | 64      |

| VTM: vortex transition memory                      | [203 (VT2)] | ✓        | 99 (9×11)     | 0.10  | 0.10         | 100  | 100    |        | 72      |

| JJ-RAM: Josephson junction RAM                     | [199]       | <b>√</b> | 484 (22×22)   |       |              |      |        | 4.5 mW | 4096    |

| RQL-RAM: reciprocal quantum logic                  | [200]       | <b>√</b> | 1452 (33×44)  |       |              |      |        |        | 1024    |

| PRAM: PTL-RAM                                      | [201, 202]  | <b>√</b> | 1452 (33×44)  |       |              |      |        |        | 512     |

| SHE-MTJ: Spin Hall effect magnetic tunnel junction | [239]       | <b>√</b> | 2470 (38×65)  | 0.10  | 2            | 1000 | 8000   |        | 16      |

| SNM: superconducting nanowire memory               | [107]       | <b>√</b> | 26.5 (5×5.3)  | 0.10  | 3            | 10   | 10     |        | 8       |

| Hybrid: JJ-CMOS                                    | [659]       | <b>√</b> |               | 2 ~ 4 | 2 ~ 4        | 100  | 100    |        | 65 536  |

Table CEQIP-6 Superconductor Memory Status

#### 2.3.2.1. JJ MEMORY

Shift registers consist of a series of bit cells that must be read or written in sequence. Applying a clock signal to the array of cells causes the data stored in each cell to shift to the next cell downstream. Examples of shift registers using SFQ logic include [120, 197, 339].

Random-access memory allows reading and writing of bits in any order. The largest demonstrated superconducting random-access memory (RAM) is only 4 Kibit (4096 bits) [198, 199].

RQL-RAM uses pure RQL logic and is under development by Northrop Grumman [200, 201, 202]. The unit cell consists of three RQL gates, including a single NDRO gate for state and readout and two gates to implement the multiplexer. A variant called PRAM combines NDRO storage with a SQUID-based readout multiplexer. Both RQL-RAM and PRAM read and write in a single clock cycle. PRAM is expected to achieve better density, speed, and power than RQL-RAM at sizes greater than 2 Kibit. RQL-RAM has been demonstrated as 128 bit (8×16) and 1024 bit (64×16) arrays [200]. PRAM with 44  $\mu$ m × 33  $\mu$ m bit cells has been demonstrated as a complete array (drivers, unit cells, sense amps) of 512 bits (16×32) [202]. The read path shared by JMRAM and PRAM has been demonstrated as a 16×32 array (decoders, drivers, unit cells, sense amplifiers, and test wrappers).

SFQ vortex transitional (VT) memory cells have been designed with sizes as small as 9  $\mu$ m  $\times$  11  $\mu$ m, fabricated in arrays using the MIT LL SFQ5ee process, and successfully demonstrated [203]. This demonstration was not a complete RAM as addressing and readout circuits were not included on the chip.

Lookup tables (LUT) have been demonstrated with 4 bits and designed with 16 bits using RSFQ circuits [204]. Multi-fluxon memory cells might allow increased storage density with an acceptable increase in circuit complexity [205].

A memory cell with 3 conventional Josephson junctions (0-junctions) and a Nb/PdNi/Nb magnetic junction ( $\pi$ -junction) has been demonstrated [206]. The  $\pi$ -junction eliminates the need to provide bias current to the memory cell. Bipolar SFQ pulse trains sent over a passive transmission line are intended to perform read and write operations. Optimization of the memory cell is required for use in arrays.

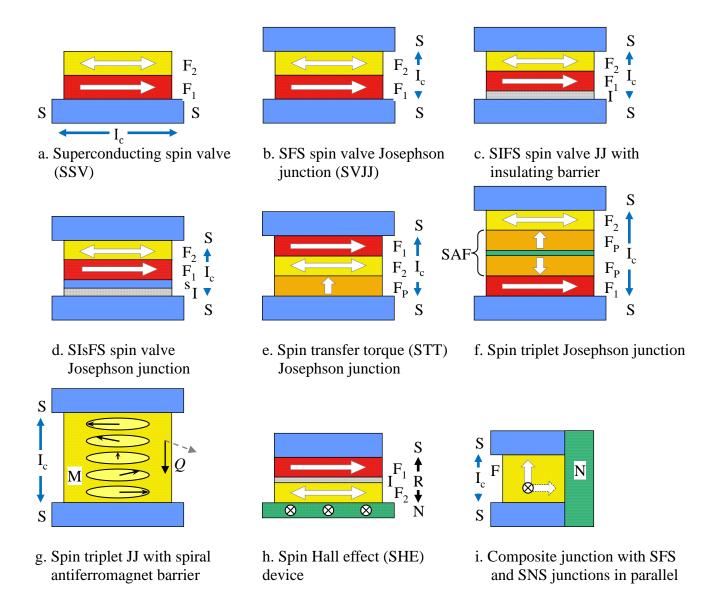

#### 2.3.2.2. MAGNETIC MEMORY